# TSC691E Integer Unit

User's Manual

for Embedded Real time 32–bit Computer (ERC32)

for SPACE Applications

# **Table of contents**

| 1. Introduction                                      | . 1  |

|------------------------------------------------------|------|

| 2. TSC691E OVERVIEW                                  | 2    |

| 2.1. SPARC RISC STANDARD FUNCTIONS :                 |      |

| 2.2. Fault Tolerant and Test Mechanism Improvements: |      |

| 2.3. Presentation of the ERC32 computing core        |      |

| 2.3.1. Concept                                       |      |

| 2.3.2. Functional Description                        |      |

| 3. Standard IU Function                              | . 4  |

| 3.1. Introduction                                    | 4    |

| 3.2. Description Of Parts                            | 5    |

| 3.3. Programming Model                               |      |

| 3.3.1. Register Windows                              |      |

| 3.3.1.1. Windowing                                   |      |

| 3.3.1.1.1. Parameter Passing                         |      |

| 3.3.1.1.2. Window Overflow and Underflow             |      |

| 3.3.1.1.3. Alternate Register Window Usage           | 9    |

| 3.3.1.2. Special Registers                           |      |

| 3.3.2. Processor States                              | . 11 |

| 3.3.3. Supervisor/User Modes                         | . 11 |

| 3.3.4. Control/Status Registers                      | . 11 |

| 3.3.4.1. Program Counters (PC and nPC)               | . 11 |

| 3.3.4.2. Processor State Register (PSR)              | . 12 |

| 3.3.4.3. Window Invalid Mask Register (WIM)          | . 14 |

| 3.3.4.4. Trap Base Register (TBR)                    |      |

| 3.3.4.5. Y Register                                  | . 15 |

| 3.3.5. Data Types                                    | . 15 |

| 3.3.5.1. Data Organization In Registers              | . 15 |

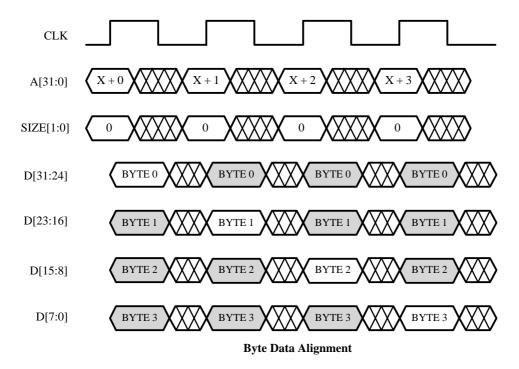

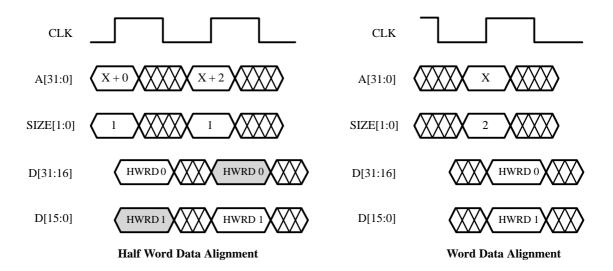

| 3.3.5.2. Data Organization In Memory                 | . 17 |

| 3.3.5.3. Extended Precision                          | . 17 |

| 3.4. Instruction Set                                 | . 18 |

| 3.4.1. Instruction Formats                           | . 18 |

| 3.4.2. Addressing                                    | . 20 |

| 3.4.2.1. Two–Register                                | . 20 |

| 3.4.2.2. Register Plus 13-Bit Immediate              | . 20 |

| 3.4.2.3. 13-Bit Immediate                            | . 20 |

| 3.4.2.4. CALL                                        | . 21 |

| 3.4.2.5. Branch                                      | . 21 |

| 3.4.2.6. ASI                                         | . 22 |

| 3.4.3. Instruction Types                             | . 22 |

| 3.4.3.1. Load/Store                                  | . 22 |

| 3.4.3.1.1. ASI                                       | . 22 |

| 3.4.3.1.2. Multiprocessing Instructions              | . 23 |

| 3.4.3.2. Arithmetic/Logical/Shift                    |      |

| 3.4.3.2.1. Register r[0]                             | . 24 |

| 3.4.3.2.2. SETHI                                     |      |

| 3.4.3.2.3. Tagged Arithmetic                         | . 25 |

| 3.4.3.3. Control Transfer                                                                                |      |

|----------------------------------------------------------------------------------------------------------|------|

| 3.4.3.3.1. Branching and the Condition Codes                                                             | . 26 |

| 3.4.3.3.2. Trap Instructions                                                                             | . 27 |

| 3.4.3.3. Calls and Returns                                                                               | . 28 |

| 3.4.3.4. Delayed Control Transfer                                                                        | . 29 |

| 3.4.3.4.1. PC and nPC                                                                                    | . 29 |

| 3.4.3.4.2. Delay Instruction                                                                             | . 29 |

| 3.4.3.4.3. Annul Bit                                                                                     | . 29 |

| 3.4.3.4.4. Delayed Control Transfer Couples                                                              | . 30 |

| 3.4.3.5. Read/Write Control Registers                                                                    | . 33 |

| 3.4.3.6. Floating-Point-Operate and Coprocessor-Operate                                                  |      |

| 3.4.3.7. Miscellaneous                                                                                   |      |

| 3.4.4. Op Codes                                                                                          |      |

| 3.4.4.1. Load/Store Instructions                                                                         |      |

| 3.4.4.2. Arithmetic/Logical/Shift Instructions                                                           |      |

| 3.4.4.3. Control Transfer Instructions                                                                   |      |

| 3.4.4.4. Read/Write Control Register Instructions                                                        |      |

| 3.4.4.5. Floating-Point/Coprocessor Instructions                                                         |      |

| 3.4.4.6. Miscellaneous Instructions                                                                      |      |

| 3.4.4.7. Opcodes In Ascending Numeric Order                                                              |      |

| 3.5. Signal Description                                                                                  |      |

| 3.5.1. Memory Subsystem Interface Signals                                                                |      |

| 3.5.1.1 A[31:0]—Address Bus (output)                                                                     |      |

| 3.5.1.2. APAR—Address Bus Parity (output)                                                                |      |

| 3.5.1.3. AOE—Address Output Enable (input)                                                               |      |

| 3.5.1.4. ASI[7:0]—Address Space Identifier (output)                                                      |      |

| 3.5.1.5. ASPAR—ASI and SIZE Parity (output)                                                              |      |

| 3.5.1.6. BHOLD—Bus Hold (input)                                                                          |      |

| 3.5.1.7. COE—Control Output Enable (input)                                                               |      |

| 3.5.1.8. D[31:0]—Data Bus (bidirectional)                                                                |      |

| 3.5.1.9.DPAR—Data Bus (ordirectional)                                                                    |      |

| 3.5.1.10. DOE—Data Output Enable (input)                                                                 |      |

| 3.5.1.11. DXFER—Data Transfer (output)                                                                   |      |

| 3.5.1.12. IFT—Instruction Cache Flush Trap (input)                                                       |      |

| 3.5.1.12. IN T—Instruction Cache Plush Trap (input)  3.5.1.13. INULL—Integer Unit Nullify Cycle (output) |      |

|                                                                                                          |      |

| 3.5.1.14. LDSTO—Atomic Load—Store (output)                                                               |      |

| 3.5.1.15. LOCK—Bus Lock (output)                                                                         |      |

| 3.5.1.16. MAO—Memory Address Output (input)                                                              |      |

| 3.5.1.17. MDS—Memory Data Strobe (input)                                                                 |      |

| 3.5.1.18. MEXC—Memory Exception (input)                                                                  |      |

| 3.5.1.19. MHOLD(A/B)—Memory Holds (inputs)                                                               |      |

| 3.5.1.20. RD—Read Access (output)                                                                        |      |

| 3.5.1.21. SIZE[1:0]—Bus Transaction Size (outputs)                                                       |      |

| 3.5.1.22. WE—Write Enable (output)                                                                       |      |

| 3.5.1.23. WRT—Advanced Write (output)                                                                    |      |

| 3.5.1.24. IMPAR—IU to MEC Control Parity (output)                                                        |      |

| 3.5.2. Floating-Point/Coprocessor Interface Signals                                                      |      |

| 3.5.2.1. CCC[1:0]—Coprocessor Condition Codes (input)                                                    |      |

| 3.5.2.2. CCCV—Coprocessor Condition Codes Valid (input)                                                  |      |

| 3.5.2.3. CEXC—Coprocessor Exception (input)                                                              |      |

| 3.5.2.4. CHOLD—Coprocessor Hold (input)                                                                  | . 56 |

|                                                                                                          |      |

| 3.5.2.5. CINS1—Coprocessor Instruction in Buffer 1 (output)           |      |

|-----------------------------------------------------------------------|------|

| 3.5.2.6. CINS2—Coprocessor Instruction in Buffer 2 (output)           |      |

| 3.5.2.7. $\overline{\text{CP}}$ —Coprocessor Unit Present (input)     | . 56 |

| 3.5.2.8. CXACK—Coprocessor Exception Acknowledge (output)             | . 56 |

| 3.5.2.9. FCC[1:0]—Floating-Point Condition Codes (input)              | . 56 |

| 3.5.2.10. FCCV—Floating-Point Condition Codes Valid (input)           | . 56 |

| 3.5.2.11. FEXC—Floating-Point Exception (input)                       |      |

| 3.5.2.12. FHOLD—Floating-Point Hold (input)                           |      |

| 3.5.2.13. FIPAR—FPU to IU Control Parity (input)                      |      |

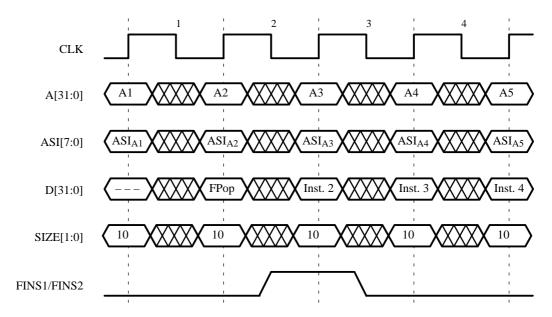

| 3.5.2.14. FINS1—Floating-Point Instruction In Buffer 1 (output)       |      |

| 3.5.2.15. FINS2—Floating-Point Instruction In Buffer 2 (output)       |      |

| 3.5.2.16. FLUSH—Floating-Point/Coprocessor Instruction Flush (output) |      |

| 3.5.2.17. FP—Floating-Point Unit Present (input)                      |      |

| 3.5.2.18. FXACK—Floating-Point Exception Acknowledge (output)         |      |

| 3.5.2.19. INST—Instruction Fetch (output)                             |      |

| 3.5.2.20. IFPAR—IU to FPU Control Parity (output)                     |      |

| 3.5.3. Interrupt and Control Signals                                  |      |

| 3.5.3.1. ERROR—Error State (output)                                   |      |

| 3.5.3.2. HWERROR—Hardware Error (output)                              |      |

| 3.5.3.3. FLOW —Enable Flow Control (input)                            |      |

| 3.5.3.4. MCERR—Comparison Error (output)                              |      |

| 3.5.3.5. 601MODE—Normal 601 Mode Operation (input)                    |      |

| 3.5.3.6. CMODE—Normal our Mode Operation (input)                      |      |

| 3.5.3.7. FPSYN—Floating-Point Synonym Mode (input)                    |      |

|                                                                       |      |

| 3.5.3.8. INTACK—Interrupt Acknowledge (output)                        |      |

| 3.5.3.9. IRL[3:0]—Interrupt Request Level (input)                     |      |

| 3.5.3.10. RESET—Integer Unit reset (input)                            |      |

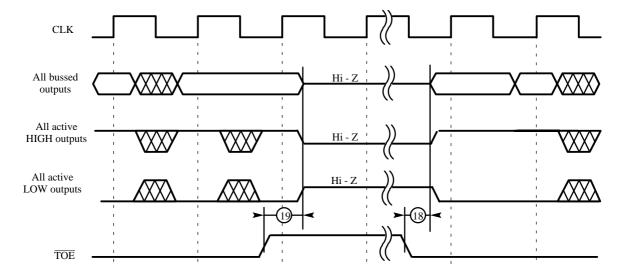

| 3.5.3.11. TOE—Test Mode Output Enable (input)                         |      |

| 3.5.3.12. HALT—Halt (input)                                           |      |

| 3.5.4. TAP signals                                                    |      |

| 3.5.4.1. TCLK—Test Clock (input)                                      |      |

| 3.5.4.2. TRST—TEST Reset (input)                                      |      |

| 3.5.4.3. TMS—Test Mode Select (input)                                 |      |

| 3.5.4.4. TDI—Test Data Input (input)                                  |      |

| 3.5.4.5. TDO—Test Data Output                                         |      |

| 3.5.5. Power and Clock Signals                                        |      |

| 3.5.5.1. CLK—Clock (input)                                            |      |

| 3.5.5.2. VCCO, VCCI, VCCT—Power (inputs)                              |      |

| 3.5.5.3. VSSO, VSSI, VSST—Ground (inputs)                             |      |

| 3.6. Pipeline and Instruction Execution Timing                        |      |

| 3.6.1.Stages                                                          |      |

| 3.6.1.1. Internal Opcodes                                             |      |

| 3.6.2. Multicycle Instructions                                        |      |

| 3.6.2.1. Register Interlocks                                          |      |

| 3.6.2.2. Branching                                                    |      |

| 3.6.3. Pipeline Freezes                                               |      |

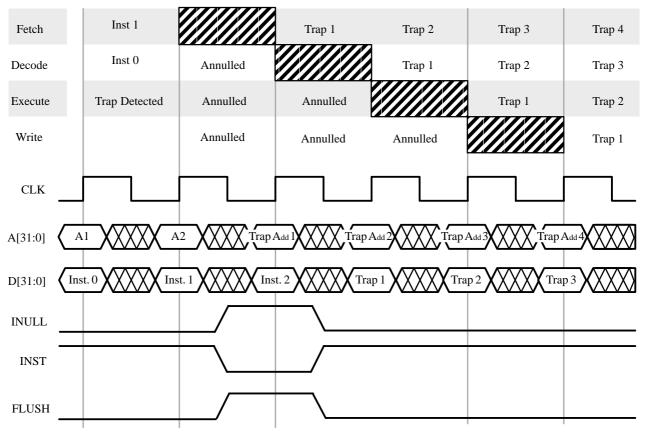

| 3.6.4. Traps                                                          |      |

| 3.7. Bus Operation and Timing                                         |      |

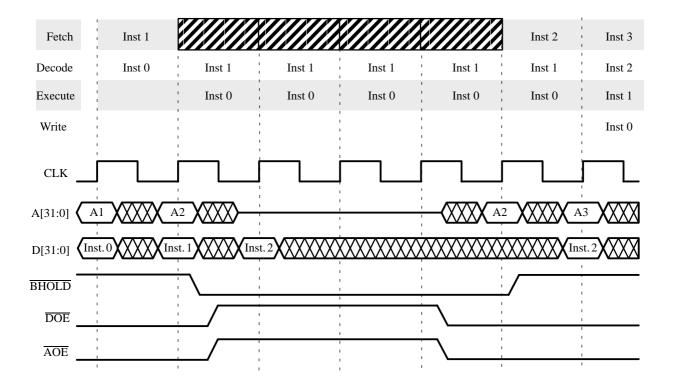

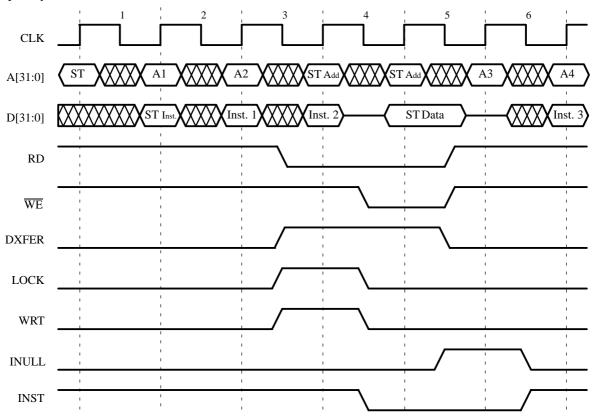

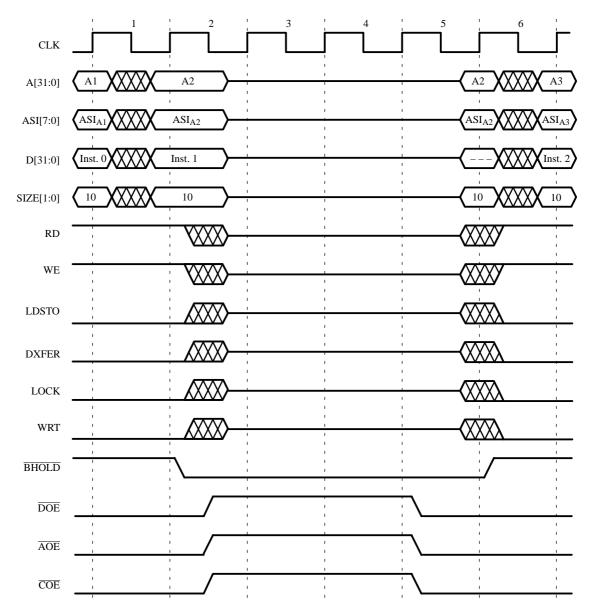

| 3.7.1. Instruction Fetch                                              | . 69 |

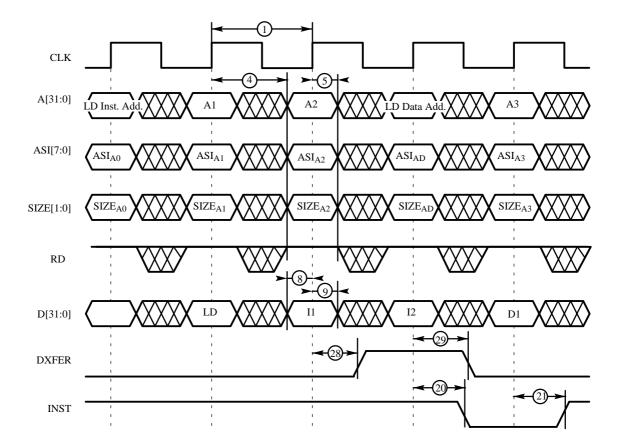

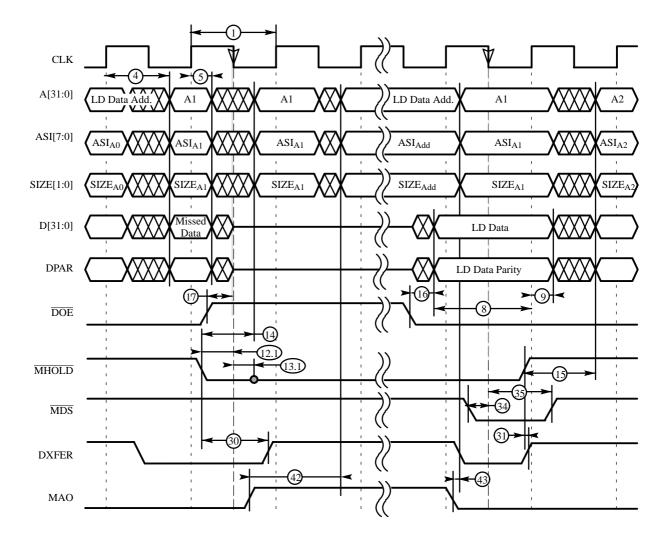

| 3.7.2. Load                                                           |      |

| 3.7.3. Load with Interlock                                            | 70   |

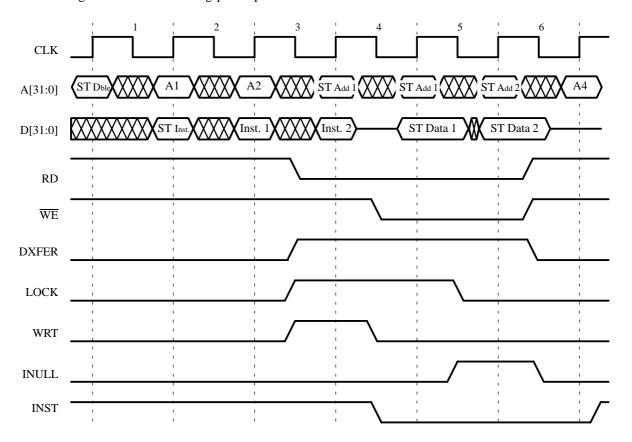

|     | 3.7.4. Load Double                       | . 71 |

|-----|------------------------------------------|------|

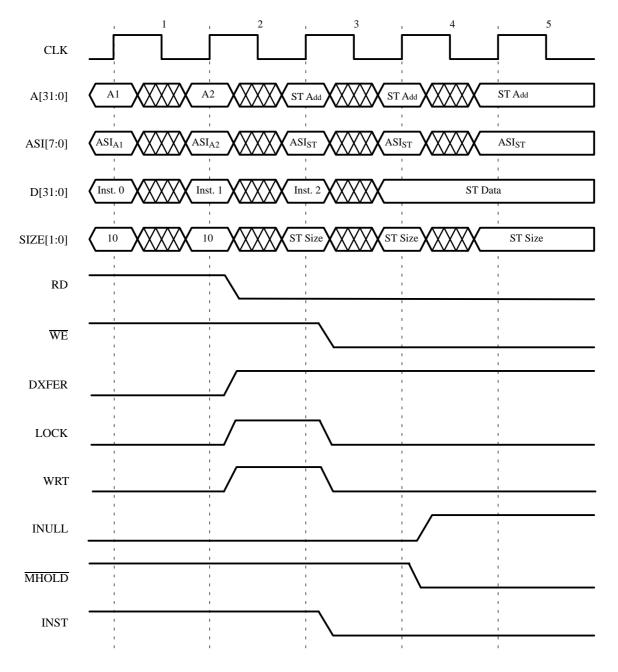

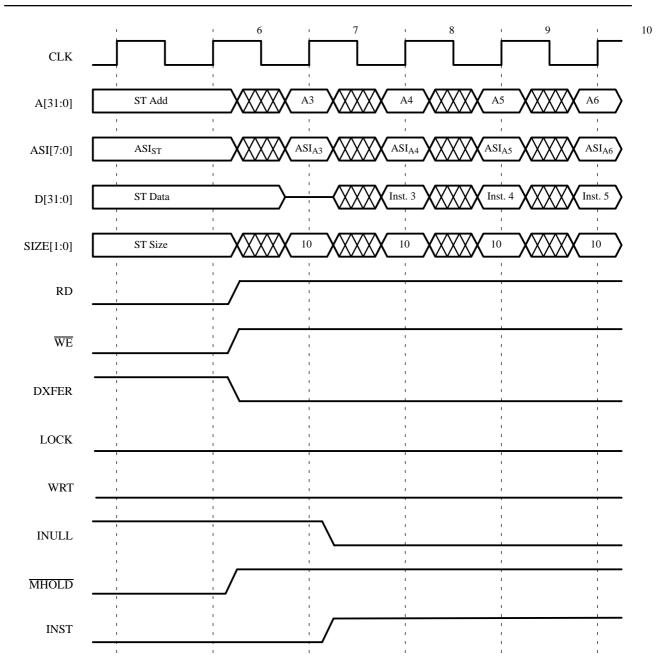

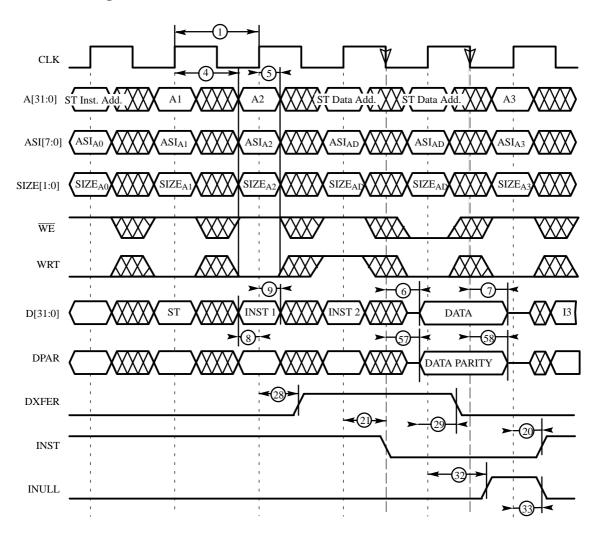

|     | 3.7.5. Store                             | . 72 |

|     | 3.7.6. Store Double                      | . 73 |

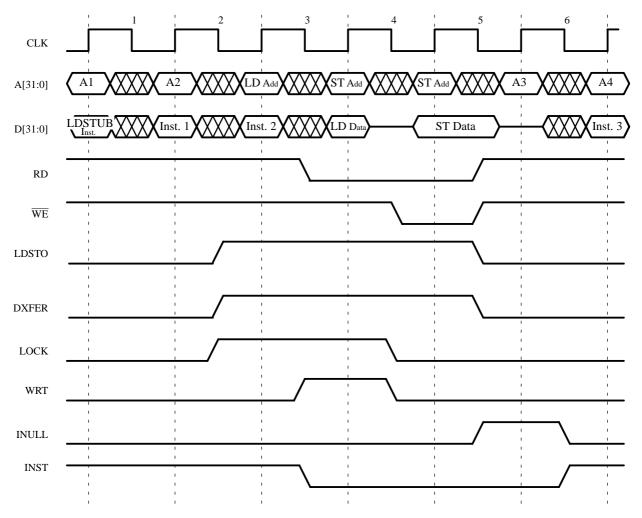

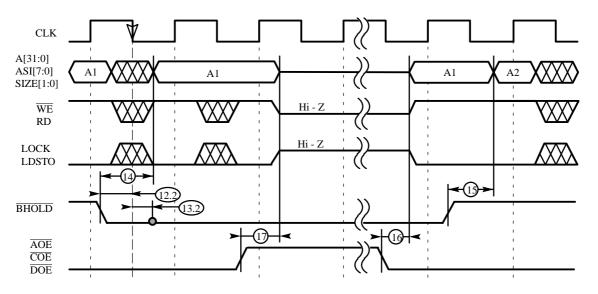

|     | 3.7.7. Atomic Load–Store                 | . 74 |

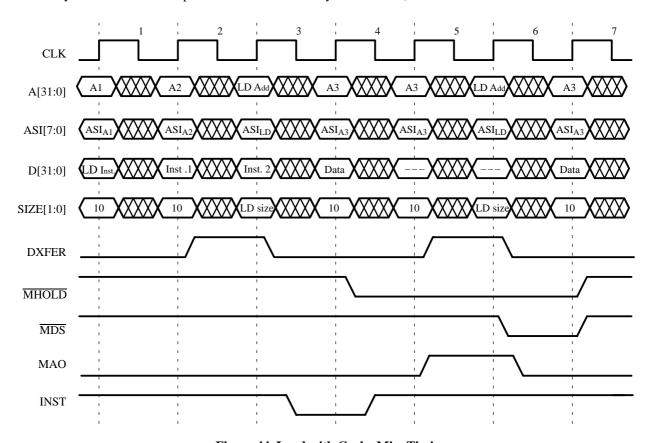

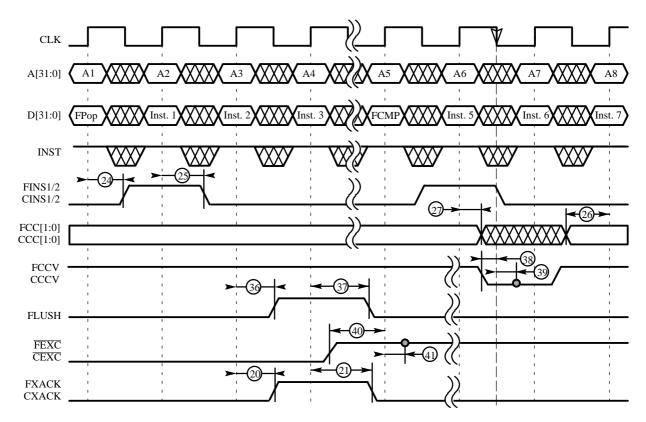

|     | 3.7.8. Floating-Point Operations         | . 75 |

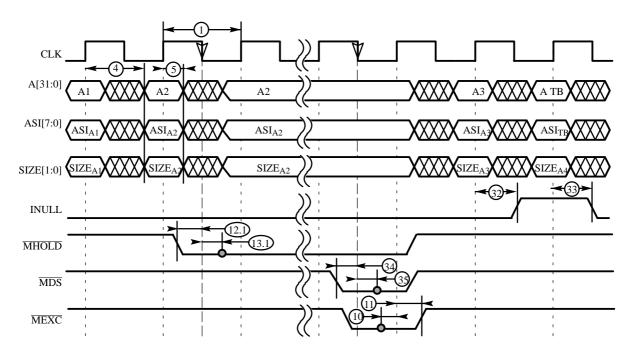

|     | 3.7.9. Bus Arbitration                   | . 76 |

|     | 3.7.10. Load with Cache Miss             | . 77 |

|     | 3.7.11. Store with Cache Miss            |      |

|     | 3.7.12. Load/Store instruction with Trap |      |

|     | 3.7.13. Memory Exceptions                |      |

|     | 3.7.14. Floating-Point Exceptions        |      |

|     | 3.7.15. Interrupts                       |      |

|     | 3.7.16. Reset Condition                  |      |

|     | 3.7.17. Error Condition                  |      |

| 3 9 | B. Exception Model                       |      |

| ٥.ر | 3.8.1. Reset                             |      |

|     | 3.8.2. Synchronous Traps                 |      |

|     | 3.8.2.1. External Signals                |      |

|     | · · · · · · · · · · · · · · · · · · ·    |      |

|     | 3.8.2.1.1. Hardware error                |      |

|     | 3.8.2.1.2. Instruction access exeption   |      |

|     | 3.8.2.1.3. Data access exception         |      |

|     | 3.8.2.2. Internal/Software               |      |

|     | 3.8.2.2.1. Illegal instruction           |      |

|     | 3.8.2.2.2. Privileged instruction        |      |

|     | 3.8.2.2.3. Fp disabled                   |      |

|     | 3.8.2.2.4. Cp disabled                   |      |

|     | 3.8.2.2.5. Window overflow               |      |

|     | 3.8.2.2.6. Window underflow              |      |

|     | 3.8.2.2.7. Memory address not aligned    |      |

|     | 3.8.2.2.8. Tag overflow                  |      |

|     | 3.8.2.2.9. Trap instruction              |      |

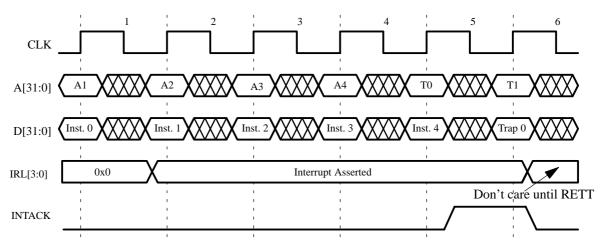

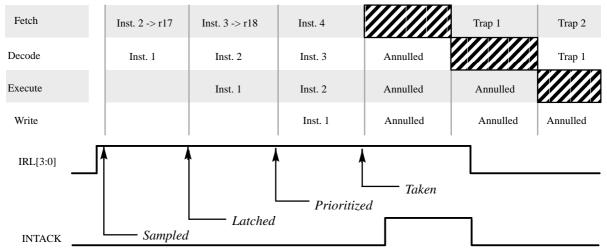

|     | 3.8.3. Interrupts (Asynchronous Traps)   | . 97 |

|     | 3.8.3.1. Priority                        |      |

|     | 3.8.3.2. Response Time                   | . 97 |

|     | 3.8.3.3.Interrupt Acknowledge            | . 99 |

|     | 3.8.4. Floating-Point/Coprocessor Traps  | . 99 |

|     | 3.8.4.1. Floating-Point Exception        | 100  |

|     | 3.8.4.2. Coprocessor Exception           | 100  |

|     | 3.8.5. Trap Operation                    | 100  |

|     | 3.8.5.1. Recognition                     | 100  |

|     | 3.8.5.2. Trap Addressing                 | 100  |

|     | 3.8.5.3. Trap Types and Priority         | 101  |

|     | 3.8.5.4. Return From Trap                | 101  |

| 3.9 | O. Coprocessor Interface                 | 102  |

|     | 3.9.1. Protocol                          |      |

|     | 3.9.1.1. Coprocessor Interface Signals   |      |

|     | 3.9.2. Register Model                    |      |

|     | 3.9.3. Exceptions                        |      |

|     |                                          |      |

| 4. Fault Tolerant and Test Mechanism                                 | 105 |

|----------------------------------------------------------------------|-----|

| 4.1. Fault Tolerant and Test Support signals                         | 106 |

| 4.1.1. Address Parity Generation:                                    |     |

| 4.1.2. Data Parity Generation/Checking:                              |     |

| 4.1.3. MEC control signal Parity Generation:                         |     |

| 4.1.4. FPU control signal Parity Generation/Checking:                |     |

| 4.1.5. Parity Checking Error Output:                                 |     |

| 4.1.6. Master/Checker Mode:                                          |     |

| 4.1.7. Test Access Port:                                             |     |

| 4.1.8. Miscellaneous:                                                |     |

| 4.2. Program Flow Control                                            |     |

| 4.2.1. Introduction                                                  |     |

| 4.2.2. Example of Program Flow Control                               |     |

| 4.3. Parity Checking                                                 |     |

| 4.3.1. Introduction                                                  |     |

| 4.3.2. Trap handling                                                 |     |

| 4.3.3. Priority within hardware traps for IU                         |     |

| 4.3.4. Parity Checking on Register File and Control/Status Registers |     |

| 4.3.5. Parity Checking on Control Signal for the FPU                 |     |

| 4.3.5.1. Output control signals                                      |     |

| 4.3.5.2. Input control signals                                       |     |

| 4.3.6. Parity Checking on Control Pads for the TSC693E (MEC)         |     |

| 4.3.6.1. Output control signals                                      | 110 |

| 4.3.6.2. Input control signals                                       |     |

| 4.3.7. Parity Checking on Control Pads for the Coprocessor           |     |

| 4.3.8. Parity Generation on ADDRESS Bus                              |     |

| 4.3.9. Parity Checking on DATA Bus                                   |     |

| 4.3.10. Non CY7C601 Mode                                             |     |

| 4.3.11. Error Type for external signals parity errors                |     |

| 4.4. Master/checker operation                                        |     |

| 4.4.1. Basic function                                                |     |

| 4.4.1.1. Master/Checker Signal description                           |     |

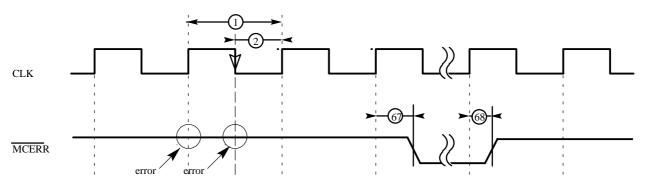

| 4.4.1.1.1. MCERR—Comparison Error (output)                           |     |

| 4.4.1.1.2.CMODE—checker Mode (input)                                 |     |

| 4.5. IEEE Standard Test Access Port & Boundary-Scan Architecture     |     |

| 4.5.1. TAP                                                           |     |

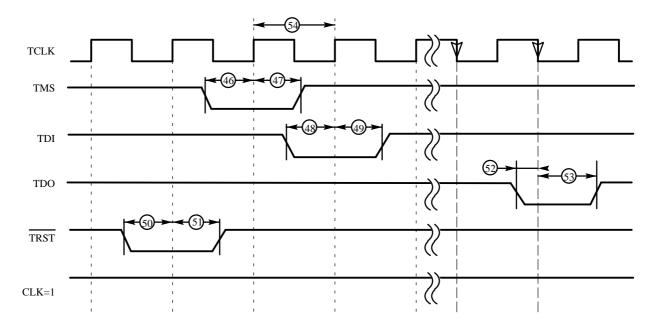

| 4.5.1.1. TCLK (input)                                                |     |

| 4.5.1.2. TMS (input)                                                 |     |

| 4.5.1.3. TDI (input)                                                 |     |

| 4.5.1.4. TRST (input)                                                |     |

| 4.5.1.5. TDO (output)                                                |     |

| 4.5.2. TAP Controller                                                |     |

| 4.5.3. The Instruction Register                                      |     |

| 4.5.3.1. Design and Construction of the instruction register         |     |

| 4.5.3.2. BYPASS Instruction                                          |     |

| 4.5.3.3. EXTEST Instruction                                          |     |

| 4.5.3.4. INTEST Instruction                                          |     |

| 4.5.3.5. SAMPLE/PRELOAD Instruction                                  |     |

| 4.5.4. The Device Identification Register                            |     |

| 4.5.5. Internal Scan Path                                            |     |

| 4.5.6. Boundary scan test register                                   |     |

| note: Dealitary sour test register                                   | 117 |

| 4.6. Interleaving register file bits                    | 115 |

|---------------------------------------------------------|-----|

| 5. Electrical and Mechanical Specification              | 116 |

| 5.1. Maximum rating and DC Characteristics              |     |

| 5.1.1. Maximum Ratings                                  |     |

| 5.1.2. Operating Range                                  |     |

| 5.1.3. DC Characteristics Over the Operating Range      |     |

| 5.1.4. Capacitance Ratings [4, 5]                       |     |

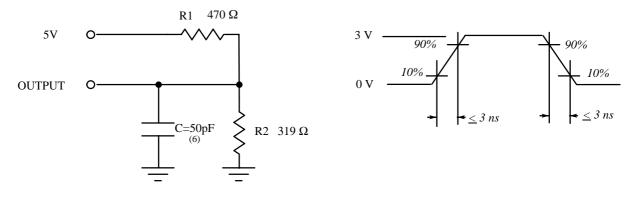

| 5.1.5. AC Test Loads and Waveforms                      |     |

| 5.2. TSC691E AC Characteristics                         |     |

| 5.2.1. AC Characteristics Over the Operation Range [1]  |     |

| 5.2.2. Waveforms                                        |     |

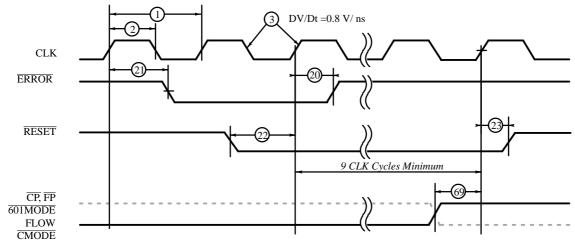

| 5.2.2.1. Clock and ERROR / RESET Timing                 |     |

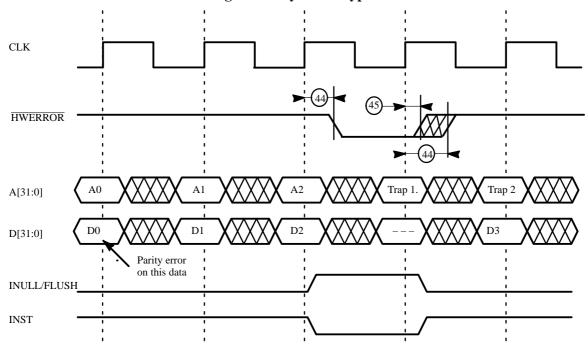

| 5.2.2.2. Clock and HWERROR Timing for Parity Error Type |     |

| 5.2.2.3. TOE De–assertion /Assertion                    |     |

| 5.2.2.4. Load Timing                                    |     |

| 5.2.2.5. Store Timing                                   | 122 |

| 5.2.2.6. Load with Cache Miss                           |     |

| 5.2.2.7. Memory Exception Timing                        |     |

| 5.2.2.8. Bus Arbitration Timing                         | 124 |

| 5.2.2.9. Floating-Point and Coprocessor Timing          |     |

| 5.2.2.10. TAP Signals                                   |     |

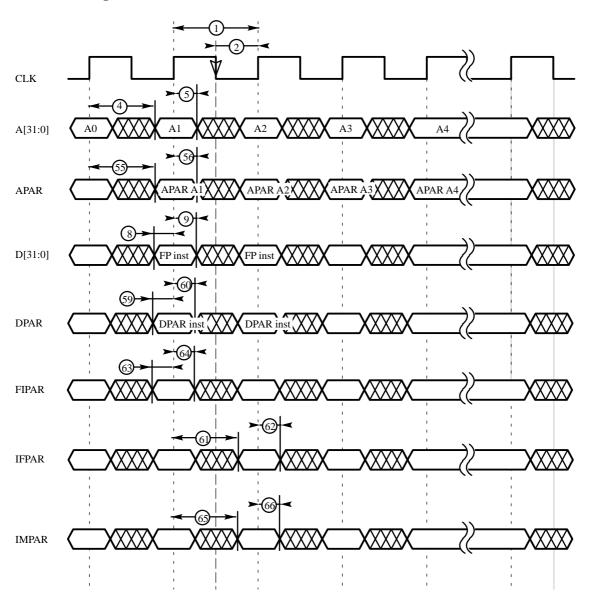

| 5.2.2.11. PARITY Signals                                | 126 |

| 5.2.2.12. MASTER/CHECKER Signals                        |     |

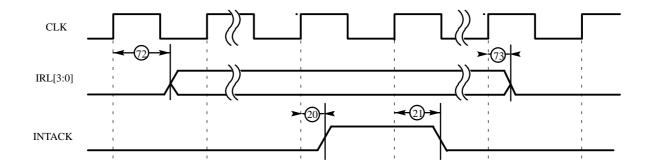

| 5.2.2.13. IRL[3:0] Signals                              |     |

| 5.2.2.14. HALT Signal timing                            |     |

| 5.3. Package Description                                |     |

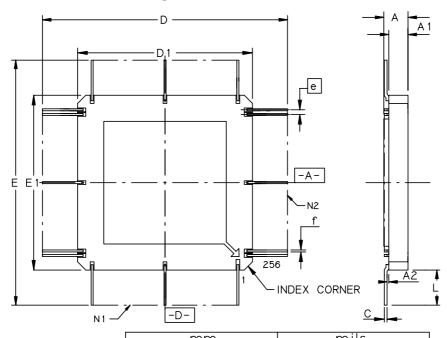

| 5.3.1. 256-Pin MQFP_F Package                           |     |

| 5.3.2. 256-Pin MQFP_F Pin Assignments                   | 129 |

# **List of Tables**

| Table 1. Register Addressing                                          |

|-----------------------------------------------------------------------|

| Table 2. Floating–Point Formats                                       |

| Table 3. Extended–Precision Floating–Point Format                     |

| Table 4. op field Coding                                              |

| Table 5. op2 Field Coding                                             |

| Table 6. ASI Assignments                                              |

| Table 7. Load/Store Instructions                                      |

| Table 8. Arithmetic/Logical/Shift Instructions                        |

| Table 9. Control Transfer Instructions                                |

| Table 10. Control Transfer Instruction Characteristics                |

| Table 11. Bicc and Ticc Condition Codes                               |

| Table 12. FBfcc Condition Codes                                       |

| Table 13. CBccc Condition Codes                                       |

| Table 14. Delayed Control Transfer Instruction Example                |

| Table 15. Effect of Annul Bit Reset (a=0)                             |

| Table 16. Effect of Annul Bit Reset (a=1)                             |

| Table 17. Effect of Annul Bit on Delay Instruction                    |

| Table 18. Delayed Control Transfer Couple Instruction Sequence        |

| Table 19. Execution of Delayed Control Transfer Couples               |

| Table 20. Read/Write Control Register Instructions                    |

| Table 21. Floating–Point–Operate and Coprocessor–Operate Instructions |

| Table 22. Miscellaneous Instructions                                  |

| Table 23. Load/Store Instruction Opcodes                              |

| Table 24. Arithmetic/Logical/Shift Instruction Opcodes                |

| Table 25. Control Transfer Instruction Opcodes                        |

| Table 26. Bicc and Ticc Condition Codes                               |

| Table 27. FBfcc Condition Codes                                       |

| Table 28. CBccc Condition Codes                                       |

| Table 29. Read/Write Control Register Instruction Opcodes             |

| Table 30. Floating–Point /Coprocessor Instruction Opcodes             |

| Table 31. Miscellaneous Instruction Opcodes                           |

| Table 32. Instruction Opcode Numeric Listing                          |

| Table 33. TSC691E External Signal Summary                             |

| Table 34. ASI Assignments                                             |

| Table 35. SIZE Bit Encoding                                           |

| Table 36. Internally Generated Opcodes                                |

| Table 37. Externally Generated Synchronous Exception Traps            |

| Table 38. Trap Type and Priority Assignments                          |

| Table 39. Error Type Assignments                                      |

| Table 40. Hardware Priority                                           |

| Table 41. Hardware error type for user registers                      |

| Table 42 Hardware error type for external signals                     |

# **List of Figures**

| Figure 1. ERC32 Architecture                                  | 3  |

|---------------------------------------------------------------|----|

| Figure 2. Integer Unit Block Diagram                          | 4  |

| Figure 3. SPARC Register Model                                | 5  |

| Figure 4. Circular Stack of Overlapping Windows               | 6  |

| Figure 5. Overlapping Windows                                 |    |

| Figure 6. Registers as Seen by a Procedure                    | 8  |

| Figure 7. Register Banks for Fast Context Switching           | 10 |

| Figure 8. Processor State Register                            | 12 |

| Figure 9. Window Invalid Mask                                 | 14 |

| Figure 10. Trap Base Register                                 | 14 |

| Figure 11. Processor Data Types                               | 16 |

| Figure 12. Byte Operand Load and Store                        | 17 |

| Figure 13. Data Organization in Memory                        | 17 |

| Figure 14. Extended–Precision Data Organization in Registers  | 18 |

| Figure 15. Extended–Precision Data Organization in Memory     | 18 |

| Figure 16. Instruction Format Summary                         | 19 |

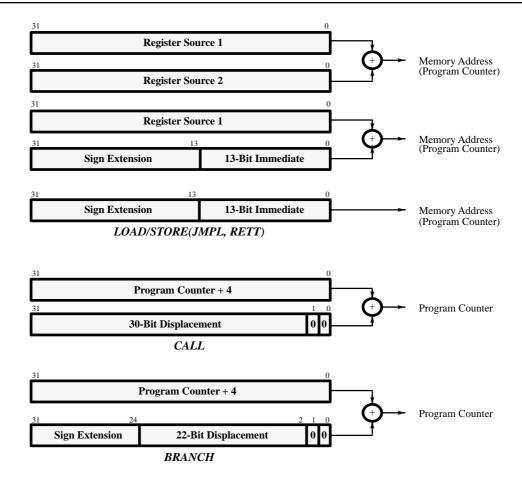

| Figure 17. Address Generation                                 | 21 |

| Figure 18. Tagged Data Example                                | 25 |

| Figure 19. Ticc Trap Address Generation                       |    |

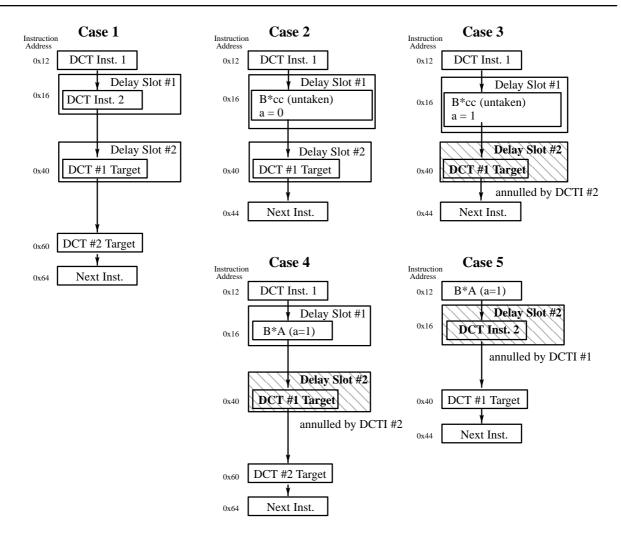

| Figure 20. Delayed Control Transfer                           |    |

| Figure 21. Delayed Control Transfer Couples                   |    |

| Figure 22. TSC691E External Signals                           |    |

| Figure 23. ASI timing with a WRPSR Instruction                |    |

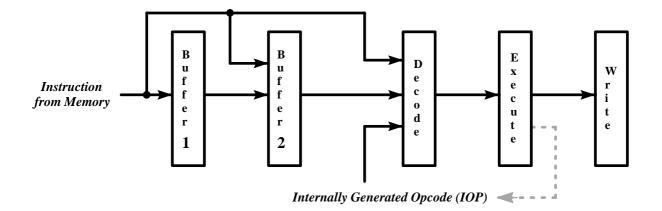

| Figure 24. Processor Instruction Pipeline                     |    |

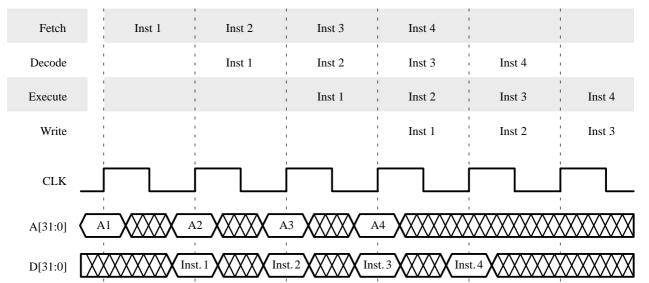

| Figure 25. Pipeline with All Single–Cycle Instructions        |    |

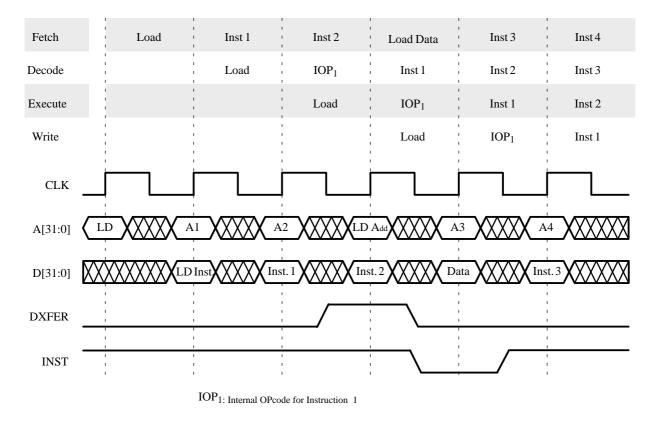

| Figure 26. Pipeline with One Double–Cycle Instruction (Load)  |    |

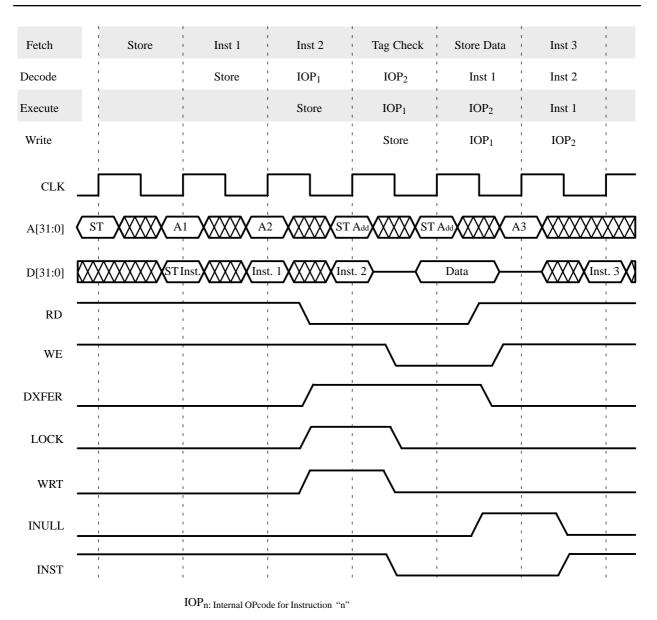

| Figure 27. Pipeline with One Triple–Cycle Instruction (Store) |    |

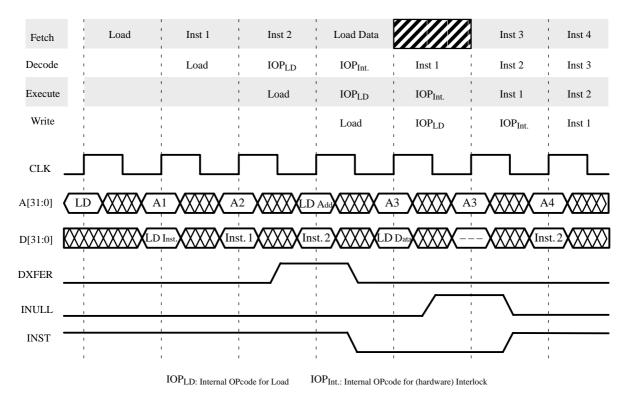

| Figure 28. Pipeline with Hardware Interlock (Load)            |    |

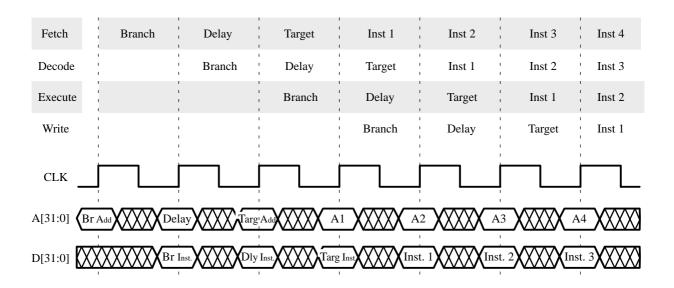

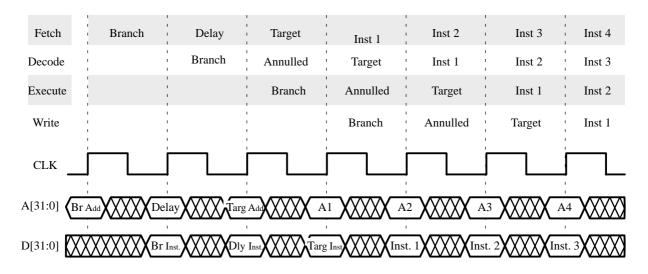

| Figure 29. Pipeline During Branch Instruction                 |    |

| Figure 30. Branch with Annulled Delay Instruction             |    |

| Figure 31. Pipeline Frozen During Bus Arbitration             |    |

| Figure 32. Pipeline Operation for Taken Trap (Internal)       |    |

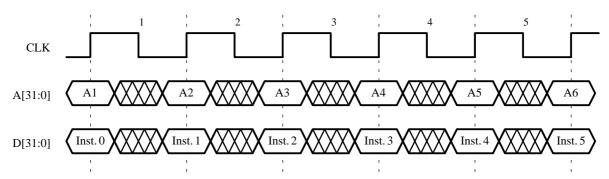

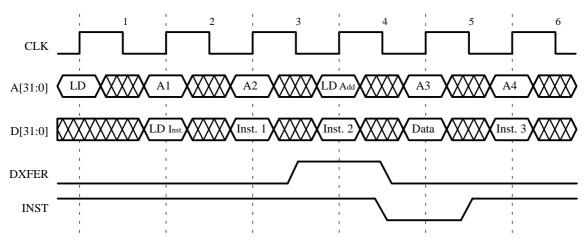

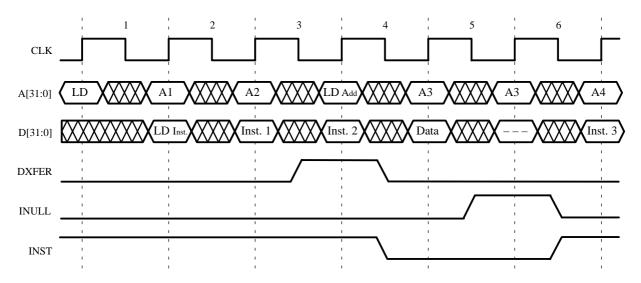

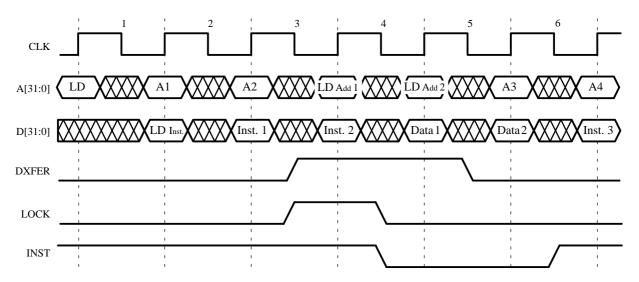

| Figure 33. Data Bus Contents During Data Transfers (1 of 2)   |    |

| Figure 34. Data Bus Contents During Data Transfers (2 of 2)   |    |

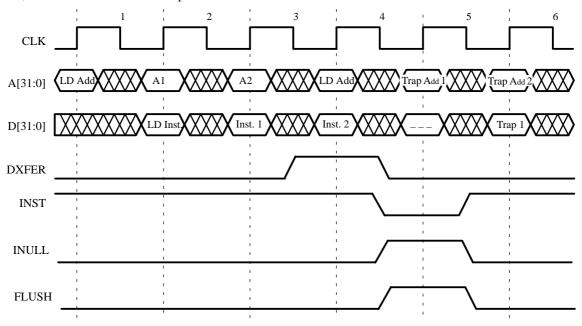

| Figure 35. Instruction Fetch                                  |    |

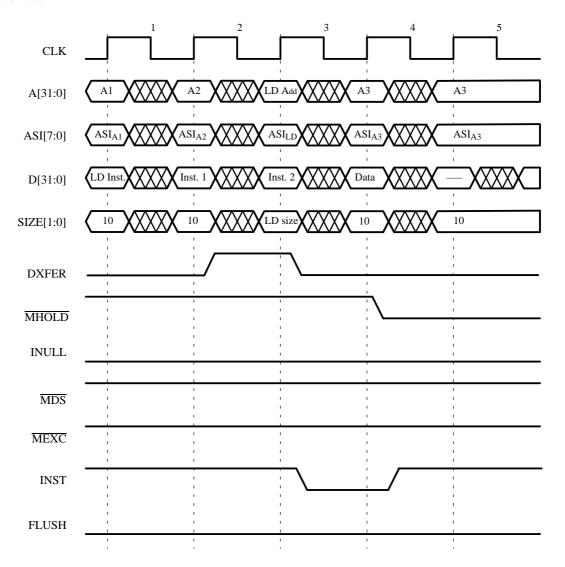

| Figure 36. Load Single Integer Timing                         | 70 |

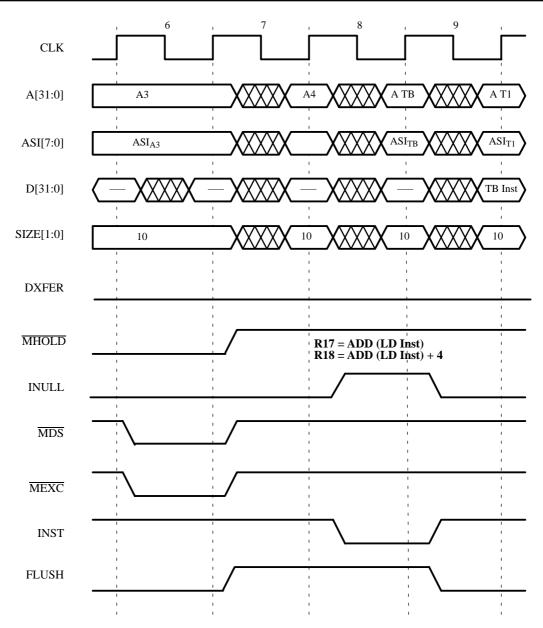

| Figure 37. Load Single with Interlock Timing                  |    |

| Figure 38. Load Double Integer Timing                         |    |

| Figure 39. Store Single Integer Timing                        |    |

| Figure 40. Store Double Integer Timing                        |    |

| Figure 41. Atomic Load–Store Timing                           |    |

| Figure 42. Floating–Point Operation Timing                    |    |

| Figure 43. Bus Arbitration Timing                             |    |

| Figure 44. Load with Cache Miss Timing                        |    |

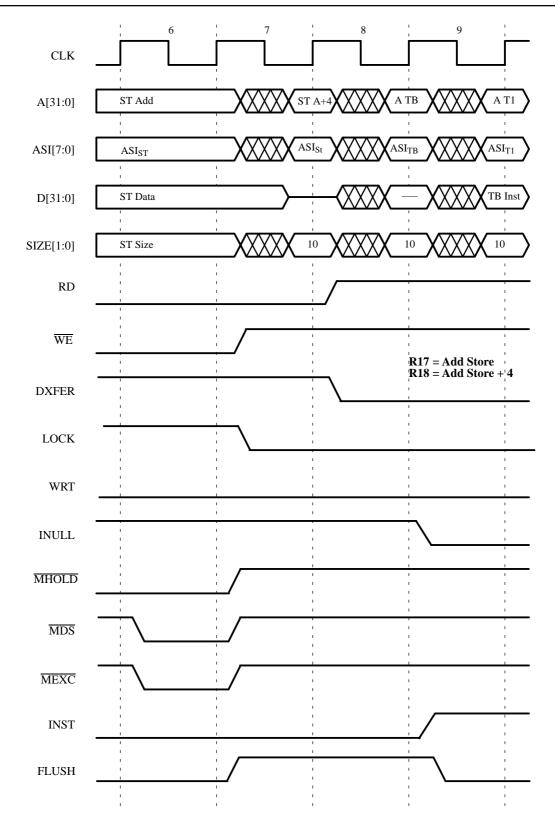

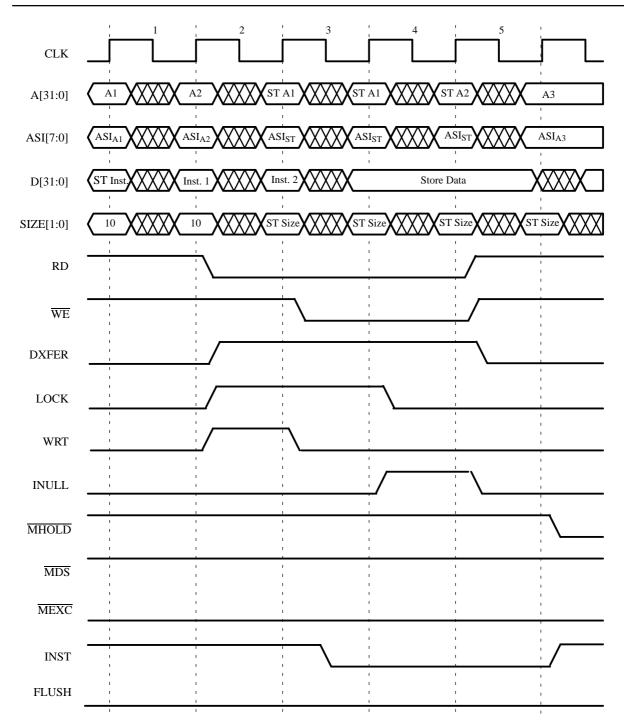

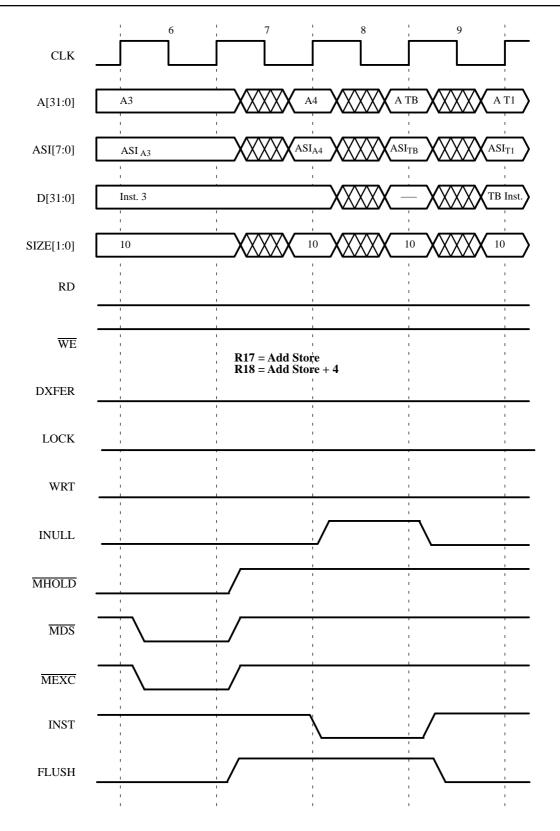

| Figure 45. Store with Cache Miss Timing (1 of 2)              |    |

| Figure 46. Store with Cache Miss Timing (2 of 2)              |    |

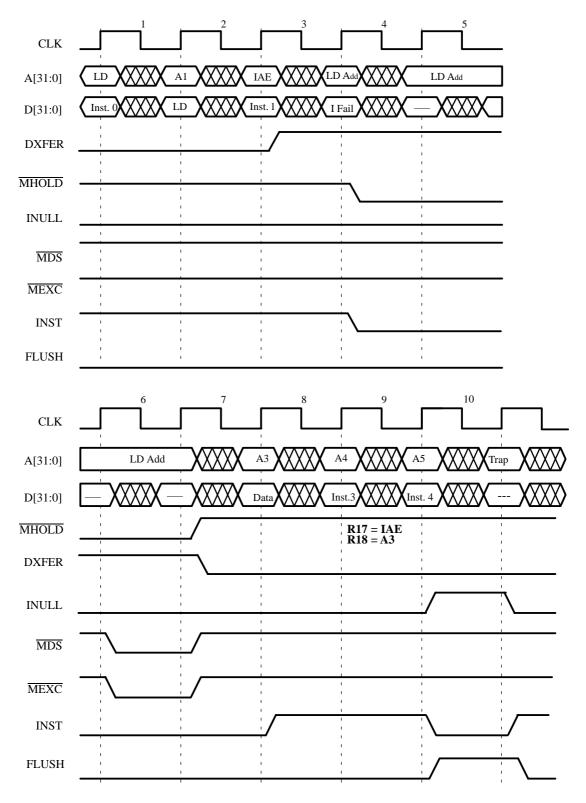

| Figure 47. Ld, LdSt, St and Swap Inst with Trap Taken         |    |

| Figure 48. Load with Memory Exception Timing (1 of 2)         |    |

| <i>y</i> ,                                                    |    |

| Figure 49. Load with Memory Exception Timing (2 of 2)                                     | 82  |

|-------------------------------------------------------------------------------------------|-----|

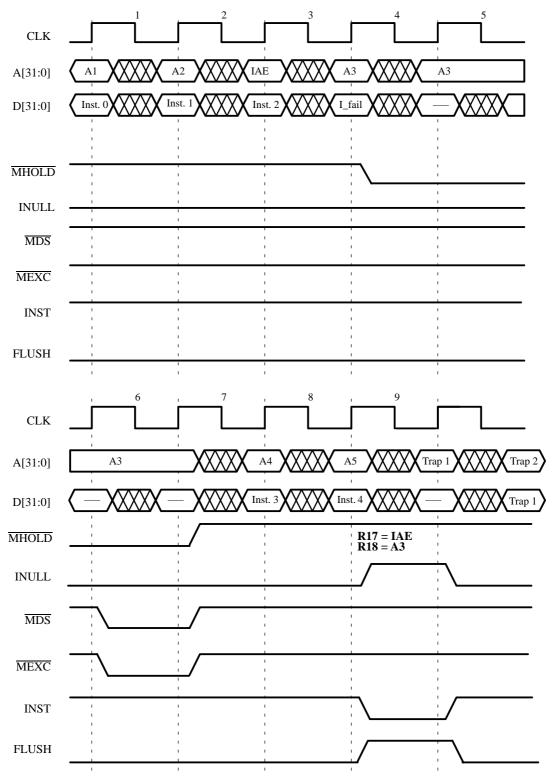

| Figure 50. Instruction Memory Access Exception Timing                                     | 83  |

| Figure 51. Instruction Memory Access Exception Timing (LD in Execute stage)               | 84  |

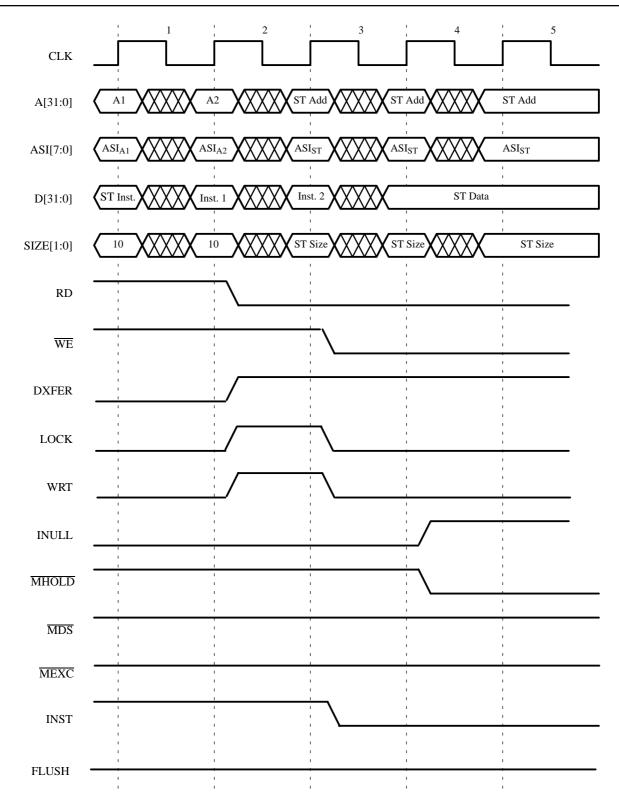

| Figure 52. Store with Memory Exception Timing (1 of 2)                                    | 85  |

| Figure 53. Store with Memory Exception Timing (2 of 2)                                    | 86  |

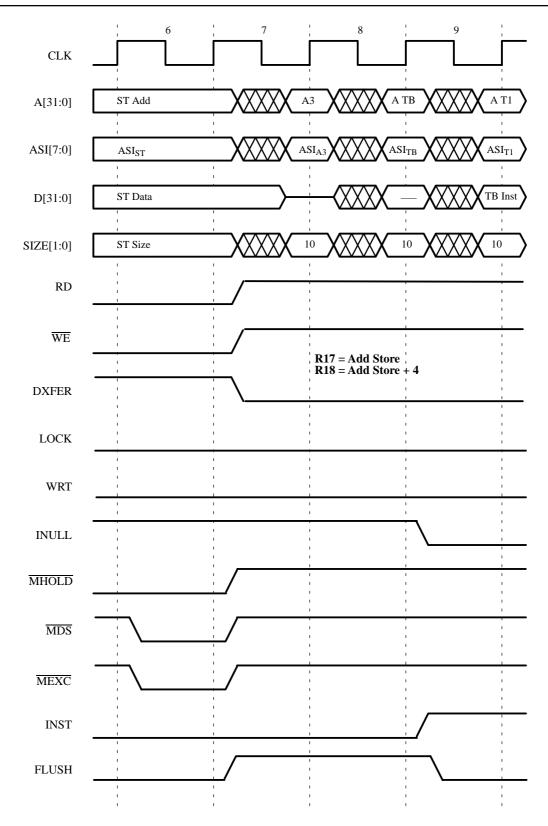

| Figure 54. Store double with Memory Exception on 1st data address (1 of 2)                | 87  |

| Figure 55. Store double with Memory Exception on 1st data address (2 of 2)                | 88  |

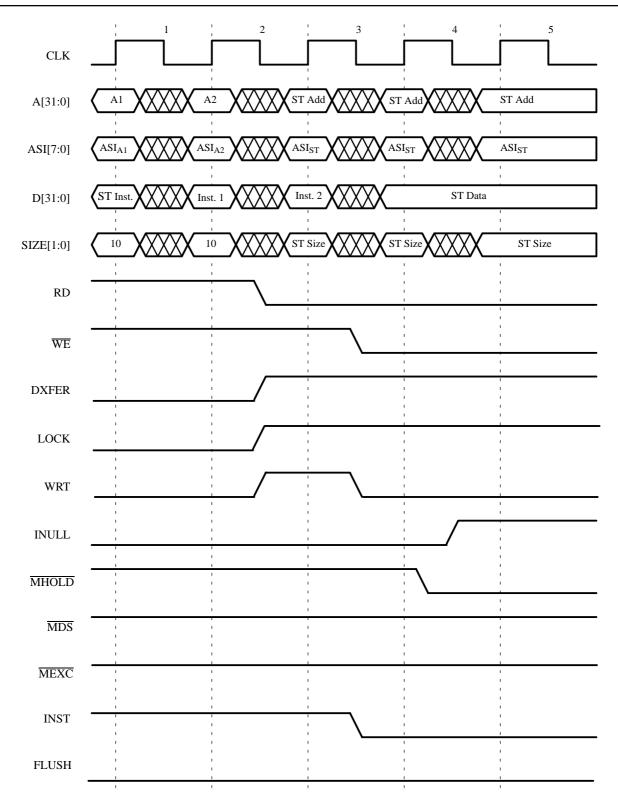

| Figure 56. Store double with Memory Exception on 2nd data address (1 of 2)                | 89  |

| Figure 57. Store double with Memory Exception on 2nd data address (2 of 2)                | 90  |

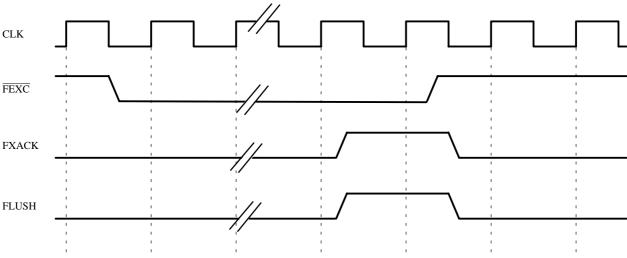

| Figure 58. Floating-Point Exception Handshake Timing                                      | 91  |

| Figure 59. Asynchronous Interrupt Timing                                                  | 91  |

| Figure 60. Power–On Reset Timing                                                          | 92  |

| Figure 61. Error/Reset Timing                                                             | 93  |

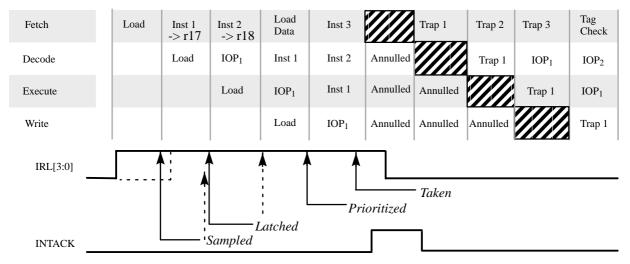

| Figure 62. Best–Case Interrupt Response Timing (one cycle instruction)                    | 97  |

| Figure 63. Double Cycles Instruction Interrupt Response Timing (ex: Load)                 | 98  |

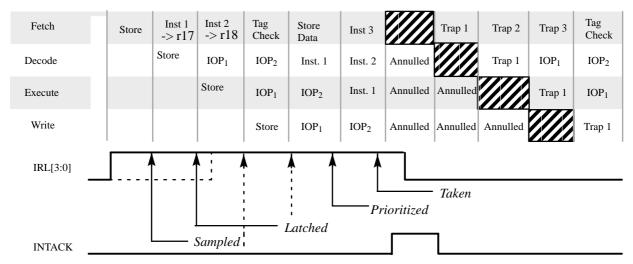

| Figure 64. Triple-Cycles Instruction Interrupt Response Timing (ex: Store)                | 98  |

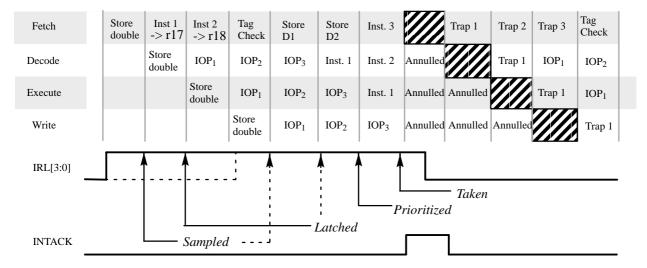

| Figure 65. Four-Cycles Instruction Interrupt Response Timing (Store Double)               | 98  |

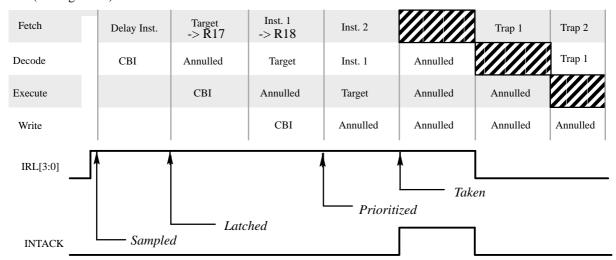

| Figure 66. Interrupt Response Timing on conditional branch instruction (B*A,a & B*cc,aNT) | 99  |

| Figure 67. Coprocessor Register Model                                                     | 103 |

| Figure 68. Fault Tolerant and Test Mechanism Block Diagram                                | 105 |

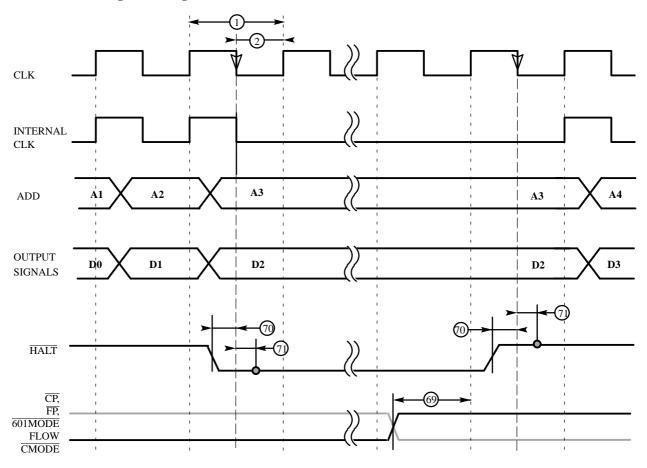

| Figure 69. Example of Program Flow Control                                                | 107 |

| Figure 70. Master/Checker Configuration                                                   | 112 |

| Figure 71. Instruction Register (IR) Cell                                                 | 113 |

| Figure 72. Boundary Scan Cell                                                             | 114 |

# **TSC691E RT Integer Unit**

# 1. Introduction

This document presents the specification of the TSC691E Radiation Tolerant Integer Unit. It is organized in three main chapters:

- Standard IU (**TSC691E**) Functions (Chapter 3)

- Fault MECHANISM and Test MECHANISM (Chapter 4)

- Electrical and Mechanical Specification (Chapter 5)

Chapter 3 presents the SPARC RISC USER'S GUIDE from Cypress Semiconductor including some adaptations due to the introduction of fault tolerant MECHANISMs, without losing the full binary compatibility with the entire SPARC V7.0 application software base.

Chapter 4 and Chapter 5 deal with the new added functions introduced in the TSC691E to improve the reliability of space applications. These new functions also do not impact the SPARC V7.0 compatibility.

# 2. TSC691E Overview

## 2.1. SPARC RISC STANDARD FUNCTIONS:

- Full binary compatibility with entire SPARC V7.0 application software base

- Architecture efficiency that sustains 1.25 to 1.5 clocks per instruction

- Large windowed register file

- Tightly coupled floating-point interface

- User/supervisor modes for multitasking

- Semaphore instructions and alternate address spaces for multiprocessing

# 2.2. Fault Tolerant and Test Mechanism Improvements:

- Parity checking on 98.7% of the total number of latches with hardware error traps

- Parity checking of address, data pads and control pads

- Program flow control

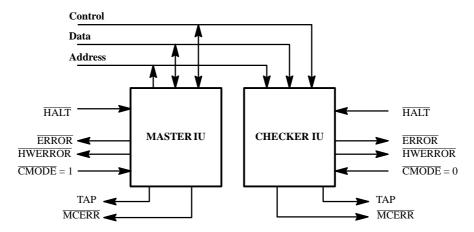

- Master/Checker operation

- IEEE Standard Test Access Port & Boundary-Scan Architecture

- Possibility to disable the bus parity checking

- Manufactured using Space hardened 0.8 µm SCMOS RT TECHNOLOGY

- Part of the ERC32 high performance 32-bit computing core

To support applications requiring an extremely high level of reliability, the following improvements were introduced in the standard SPARC RISC processor TSC691E:

- Several independent fault detection MECHANISMs to support the design of fault tolerant systems

- Such as odd parity checking, Program Flow Control and Master/Checker operations.

- Support of sophisticated PC board level test using the IEEE Standard Test Access Port and

- Boundary Scan Architecture

- Hardening of the process by construction, applying restricted full static CMOS design rules for

- all critical blocks of the circuit such as register file, PLAs, ROMs etc...

- Hardened device processing using the 0.8 µm SCMOS-RT TECHNOLOGY.

Thanks to careful handling of the improvements, the introduced modifications have neither reduced the performance of the device nor changed the full binary compatibility with the entire SPARC V7.0 application software.

# 2.3. Presentation of the ERC32 computing core

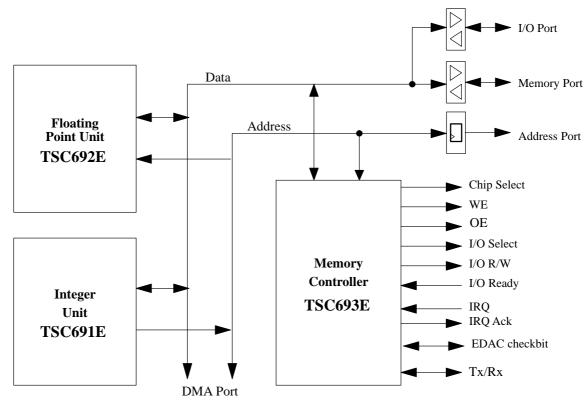

The TSC691E Integer Unit is, with the TSC692E Floating Point Unit and the TSC693E Memory controller, a part of the ERC32 computing core.

#### **2.3.1.** Concept

The objective of the ERC32 is to provide a high performance 32-bit computing core, with which computers for on-board embedded real-time applications can be built. The core will be characterized by low circuit complexity and power consumption. Extensive concurrent error detection and support for fault tolerance and reconsideration will also be emphasized.

In addition to the main objective the ERC32 core should be possible to use for performance demanding research applications in deep space probes. The radiation tolerance and error masking are therefore important. For the real-time applications the system might be fail-operational rather than fail-safe. By including support for reconfiguration of the error-handling the different demands from the applications can be optimized for the best purpose in each case.

The ERC32 will be used as a building block only requiring memory and application specific peripherals to be added to form a complete on-board computer. All other system support functions are provided by the core.

# 2.3.2. Functional Description

The ERC32 incorporates the followings functions:

- Processor, which consists of one integer unit (IU-TSC691E) and one floating point unit (FPU-TSC692E). The processor includes concurrent error detection facilities.

- Memory controller (MEC-TSC693E), which is a unit consisting of all necessary support functions such as memory

control and protection, EDAC, wait state generator, timers, interrupt handler, watch dog, UARTs and test and debug

support. The unit also includes concurrent error detection facilities.

- Oscillator (optional).

- Buffers necessary to interface with memory and peripherals.

Figure 1 schematically shows the ERC32 architecture and external functions added to form a complete system.

Figure 1. ERC32 Architecture

# 3. Standard IU Function

## 3.1. Introduction

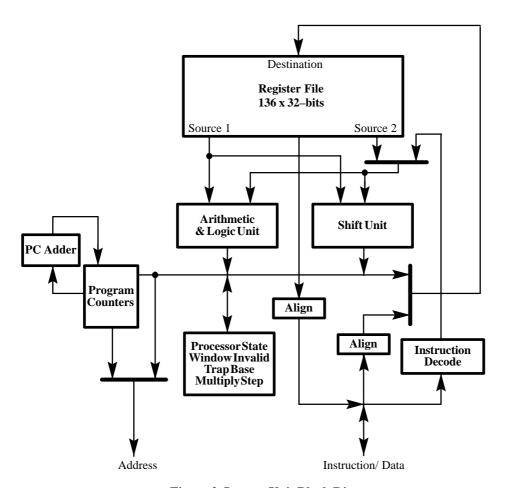

This section describes the workings of the TSC691E RT Integer processing Unit (IU), the main computing engine in the SPARC architecture. The TSC691E is based on the SPARC 32-bit RISC architecture, which defines a processor capable of execution at a rate approaching one instruction per clock cycle. The TSC691E supports a tightly-coupled Floating-Point coprocessor Unit (FPU) and a second, system-specific coprocessor, all three of which may operate concurrently. The TSC691E executes all instructions except floating-point-operate and coprocessor-operate instructions.

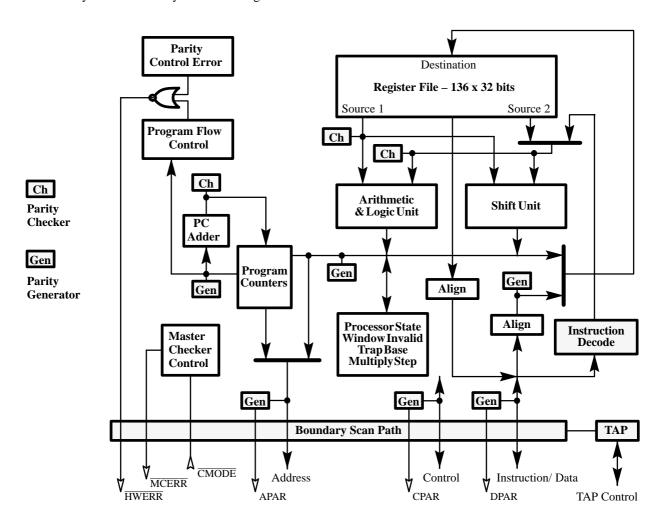

A block diagram of the TSC691E is shown in Figure 2. The processor is organized around the ALU and the shift unit. These are both two-operand units, accepting 32-bit information from either source 1 or source 2 of the register file, the program counters, or the instruction decoder. ALU or shift unit results may be passed to the register file, address bus, program counters, control registers, or back to themselves. One of the characteristics of the SPARC load/store architecture is that neither the ALU nor the shift unit directly pass results to the instruction/data bus. Memory data moves in and out of the register file through alignment units to and from the instruction/data bus. Instructions are taken directly from the bus and fed to a four-stage instruction pipeline.

Figure 2. Integer Unit Block Diagram

The SPARC architecture uses a "windowed" register file model in which the file is divided up into groups of registers called windows. This windowed register model simplifies compiler design, speeds procedure calls, and efficiently supports A/I programming languages such as Prolog, LISP and Smalltalk.

A unique pair of coprocessor interfaces and a common connection to the system data and virtual address busses form the physical interface between the IU, the FPU, and a coprocessor. The coprocessor interfaces provide the synchronization and error handling that enable all three processors to operate concurrently. A common interface to the virtual address bus and data bus permits the IU to provide all addresses for floating—point and coprocessor load and store instructions.

# 3.2. Description Of Parts

The integer unit TSC691E contains a 136 x 32 register file divided into eight overlapping windows. It is supplied in 256-pins MQFP packages, which allows 32-bit address and data busses, an eight-bit ASI bus, a number of control lines, and floating-point–coprocessor, second coprocessor interfaces and 29 signals supporting fault tolerance and test MECHANISM.

# 3.3. Programming Model

This section describes the TSC691E's register model, register window MECHANISM, processor states, supervisor/user modes, control/status registers, and data types. The concepts and properties explained here are central to an understanding of the TSC691E's operation.

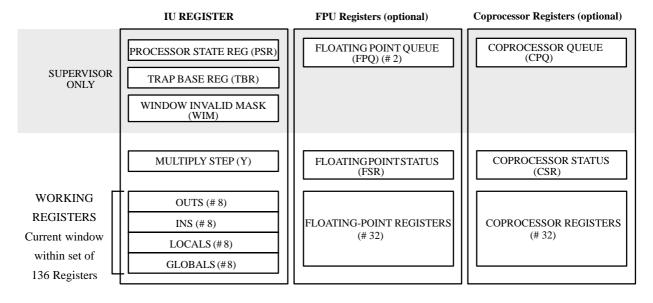

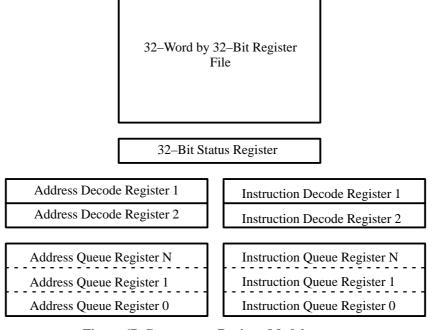

The register set shown in Figure 3 is a snapshot of the registers the TSC691E sees at any given moment. The working registers constitute the current window on the register file. Registers within the shaded area are accessible only in the supervisor mode.

Figure 3. SPARC Register Model

Working registers are used for normal operations and are called r registers in the TSC691E, f registers in the FPU, and c registers in the coprocessor. The various control/status registers keep track of and/or control the state of each processor.

### 3.3.1. Register Windows

The 136 r registers of the TSC691E are 32–bits wide and are divided into a set of 128 window registers and a set of eight global registers. The 128 window registers are grouped into eight sets of 24 r registers called windows.

Table 1. Register Addressing

| Register numbers | Name    |

|------------------|---------|

| r[24] to r[31]   | ins     |

| r[16] to r[23]   | locals  |

| r[8] to r[15]    | outs    |

| r[0] to r[7]     | globals |

The SPARC architecture supports a maximum of 32 windows. The currently active window (the window visible to the programmer) is identified by the Current Window Pointer (CWP), a 5-bit field in the Processor State Register (PSR) (see Section 3.3.4.2).

At any given time, a program can address 32 active registers: 24 window registers and the eight *globals*. By software convention, the window registers are divided into 8 *ins*, 8 *locals*, and 8 *outs*. Registers are addressed as shown in Table 1.

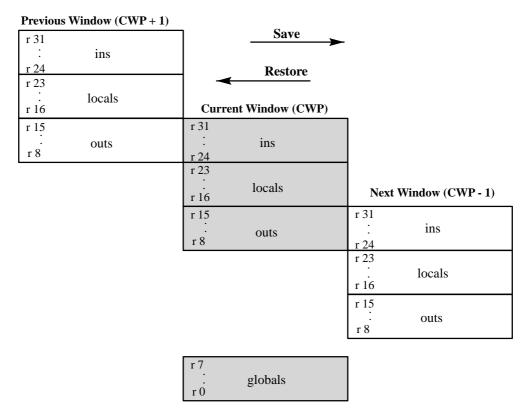

The current window pointer (CWP) acts as an index pointer within the stack of 128 window registers. Changing the current window pointer by one offsets *r* register addressing by 16. Since 24 *r* registers can be addressed by a single CWP value, incrementing or decrementing the CWP results in an eight register overlap between windows. This overlap of window registers is used to pass parameters from one window to the next.

#### **3.3.1.1.** Windowing

The register file is implemented as a circular stack, with the highest numbered window joined to the lowest. In the TSC691E, window 7 adjoins window 0 (see Figure 4).

Figure 4. Circular Stack of Overlapping Windows

Figure 5. Overlapping Windows

Note that each window shares its *ins* and *outs* with adjacent windows (refer to Figure 5). *Outs* from a previous window (CWP + 1) are the *ins* of the current window, and the *outs* of the current window are the *ins* of the next window (CWP - 1). While only adjacent windows share *ins* and *outs*, *globals* are shared by all windows. A window's *locals*, on the other hand, are not shared at all, belonging only to that window.

After power—on reset, the state of the current window pointer and the WIM register (see Section 3.3.4.3) are undefined. The power—on reset trap routine must initialize the CWP and WIM register for correct operation.

#### 3.3.1.1.1. Parameter Passing

Register window overlap provides an efficient means of passing parameters during procedure calls and returns. One method of implementing a procedure call that takes advantage of the overlap is to have the calling procedure move the parameters to be passed into its *outs* registers, then execute a CALL instruction. A SAVE instruction then decrements the CWP to activate the next window. The calling procedure's *outs* become the called procedure's *ins*, making the passed parameters directly accessible.

When a called procedure is ready to return results to the procedure that called it, those results are moved into its *ins* registers and it then executes a return, usually with a JMPL instruction. A RESTORE instruction increments the CWP to activate the previous window. The called procedure's *ins* are still the calling procedure's *outs*; thus the results are available to the calling procedure. Note that the terms *ins* and *outs* are defined relative to calling, not returning.

If the calling procedure must pass more parameters than can be accommodated by the *outs* and *globals*, the additional parameters must be passed on the memory stack. One method of handling the stack pointer is to dedicate an *out* register in the current window to hold the stack pointer (see Figure 6). After a call, this pointer (which is now in an *ins* register) can be used as the frame pointer for the called procedure. The SAVE instruction, in addition to decrementing the CWP, also performs an ADD using registers from the current window and placing the result in a register in the next window. This feature can be used to set a new stack pointer for the called procedure from the old pointer in the calling procedure. RESTORE also performs an ADD, using registers in the current window and placing the result in the previous window.

|          | r31 | (i7) return address       |

|----------|-----|---------------------------|

|          | r30 | (FP) frame pointer        |

|          | r29 | (i5) incoming param reg 5 |

| in       | r28 | (i4) incoming param reg 4 |

| iri      |     |                           |

|          | r27 | (i3) incoming param reg 3 |

|          | r26 | (i2) incoming param reg 2 |

|          | r25 | (i1) incoming param reg 1 |

|          | r24 | (i0) incoming param reg 0 |

|          | r23 | (17) local 7              |

|          | r22 | (16) local 6              |

|          | r21 | (15) local 5              |

| local    | r20 | (14) local 4              |

|          | r19 | (13) local 3              |

|          | r18 | (12) local 2              |

|          | r17 | (11) local 1              |

|          | r16 | (10) local 0              |

|          | r15 | (o7) temp                 |

|          | r14 | (SP) stack pointer        |

|          | r13 | (o5) outgoing param reg 5 |

| out      | r12 | (o4) outgoing param reg 4 |

|          | r11 | (o3) outgoing param reg 3 |

|          | r10 | (o2) outgoing param reg 2 |

|          | r9  | (o1) outgoing param reg 1 |

|          | r8  | (o0) outgoing param reg 0 |

|          | r7  | (g7) global 7             |

|          | r6  | (g6) global 6             |

|          | r5  | (g5) global 5             |

| global   | r4  | (g4) global 4             |

| Č        | r3  | (g3) global 3             |

|          | r2  | (g2) global 2             |

|          | r1  | (g1) global 1             |

|          | r0  | (g0) 0                    |

|          | f31 | floating-point value      |

| floating | :   | :                         |

| point    | •   |                           |

|          | f0  | floating-point value      |

|          |     |                           |

Figure 6. Registers as Seen by a Procedure

### 3.3.1.1.2. Window Overflow and Underflow

No matter how many windows a register file has, it is possible that at some point the program will try to use more than are available. Since the register file is a circular stack, something must be done to prevent overwriting the oldest window as the stack wraps around.

The TSC691E handles this by allowing bits in the Window Invalid Mask (WIM) register to be set, which are used to mark windows that will trigger an underflow or overflow trap (see Section 3.3.4.3). If a SAVE instruction points the

CWP to a marked window, a window overflow trap is generated. This means that in the TSC691E, only seven of the eight windows are available for calls, because the last window must be saved for the trap handler. However, since a typical overflow trap handler would transparently save one or more of the oldest windows to memory, the program sees an apparently infinite number of windows.

The TSC691E automatically decrements the CWP upon encountering a trap. This happens without generating another window overflow trap, regardless of the state of the WIM register. By setting at least one window as masked by the WIM register, the system is assured of at least one window for use by the trap handler.

A RESTORE instruction will cause a window underflow trap if it attempts to restore to a window invalidated by the WIM register. Execution of a return from Trap (RETT) instruction under the same circumstances will also generate an under trap. SAVE, RESTORE, and RETT always check the WIM register before completing their actions.

As an example, in Figure 4, if the procedure using the window labeled w0 executes a CALL and SAVE sequence, a window overflow trap will occur (assuming WIM bit 7 is set). The overflow trap handler may safely use only the *locals* of w7, because w7's *ins* are w0's *outs* and w7's *outs* are w6's *ins*.

Active window = 0 CWP = 0Previous window = 1 CWP+1 = 1Next window = 7 CWP-1 = 7

Trap window = 7  $WIM = 10000000_{(base 2)}$

The overflow trap handler is responsible for saving one or more of the least recently used windows to the memory stack. Simulations of register file management methods show that saving and restoring one window at a time is the simplest and most effective algorithm for handling overflow and underflow. The stack pointer to the window-save area must be aligned to a word boundary in valid memory and, for efficiency, should be doubleword aligned. This is because it is faster to load and store doublewords than to load and store words.

A linear sequence of doubleword loads and stores is also used to speed up context switches. In a context switch, only the windows containing valid data are saved, and on average this is about half the number of TSC691E windows, minus one for the reserved trap window.

#### 3.3.1.1.3. Alternate Register Window Usage

Although the windowing layout is particularly well suited to procedure calls and returns, hardware does not force their use for that purpose alone. Except for the eight-register overlap and the partial fixing of the function of several registers by the instruction set (see Section 3.3.1.2), register windows can be viewed and manipulated as needed to fit the application at hand.

For example, the register set can be treated as a flat register file. Access to any particular register in any window is obtained by writing its window value into the current window pointer located in the processor state register. Moreover, windows naturally segment registers into blocks that could be dedicated to specific purposes and accessed through the CWP. Register saving and parameter passing could be done with a standard push/pop stack in memory, although this would substantially increase bus traffic.

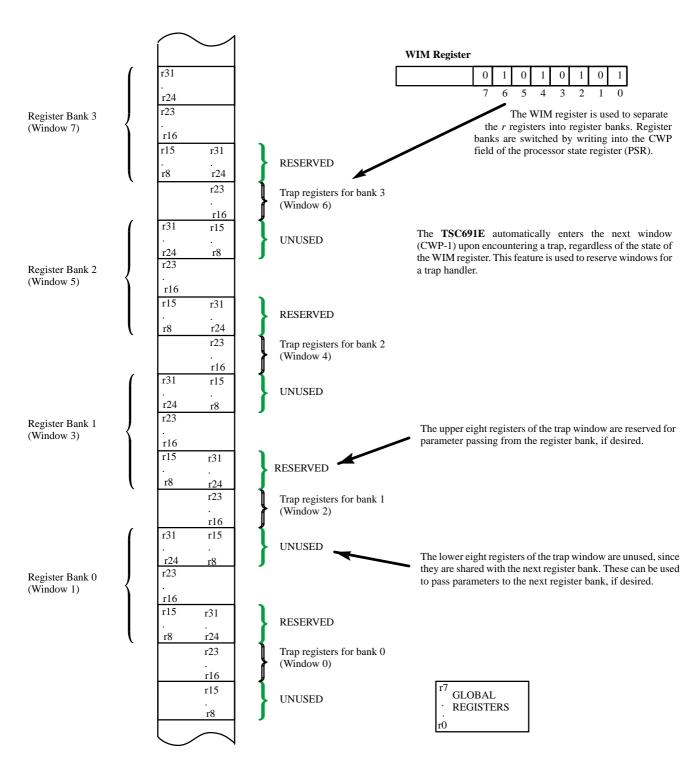

For real-time and embedded controller systems, where fast context switching may be more important than procedure calling, the register file can easily be divided into banks of registers separated by trap handling windows set up by the WIM register (see Section 3.3.4.3). Switching from one register bank to another is accomplished by writing to the CWP field of the processor state register. Figure 7 shows the TSC691E register file divided into four banks, each with its own trap handler window of eight local registers. *Globals* are accessible by all processes.

#### 3.3.1.2. Special Registers

In general, the window registers seen at any given time can be used in any manner desired, while keeping in mind that windows overlap at both ends. However, the instruction set does fix the use of r[0] and partially fixes the use of r[15].

Global register r[0] always returns the value 0 when read, making the most frequently used constant easily available at all times. In addition, when addressed as a destination operand, r[0] discards the value written to it.

The CALL instruction writes its own address into register r[15] (*out* register 7) of the calling procedure's window. If a SAVE instruction then activates a new window, r[15] of the old window becomes r[31] (*in* register 7) of the new window and serves as the return address to the calling procedure. However, if the register is needed for some other purpose, the return address can be saved to a stack or simply overwritten.

Figure 7. Register Banks for Fast Context Switching

Two other registers are also used by hardware to save information during a trap. Registers r[17] and r[18] (*locals* 1 and 2) of the trap window (not the trapping procedure's window) are used to save the contents of the program counters (PC and nPC) at the time the trap is taken. Because the trap window *locals* are all a trap handler is allowed to use (unless it saves to the system stack), this limits the trap handler's usable registers to six.

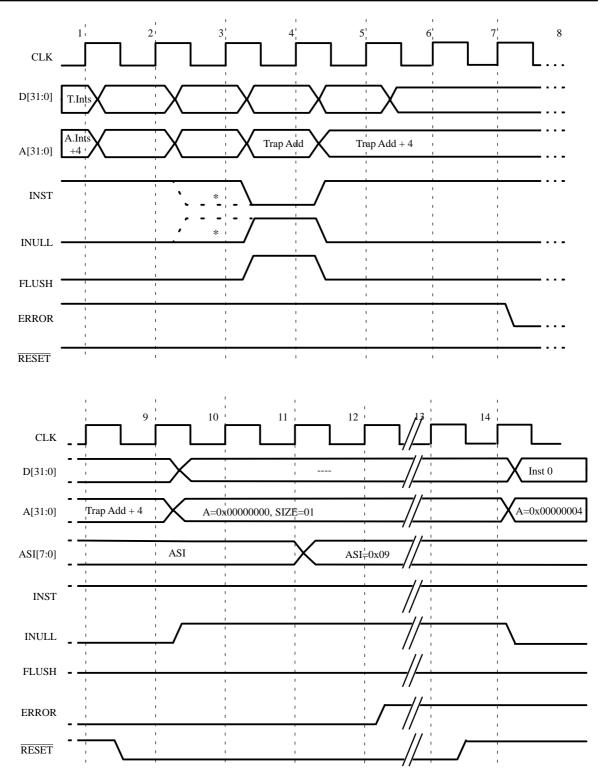

#### 3.3.2. Processor States

The TSC691E is always in one of three possible states: execute mode, reset mode, or error mode. Execute mode is the normal operating mode.

The processor enters error mode (at which point it halts and asserts  $\overline{ERROR}$ ) if a synchronous trap is generated while traps are disabled (see Section 3.8). The TSC691E remains in error mode until the  $\overline{RESET}$  signal is asserted, whereupon it enters reset mode. The external system is responsible for asserting  $\overline{RESET}$  whenever the error mode signal,  $\overline{ERROR}$ , is detected.

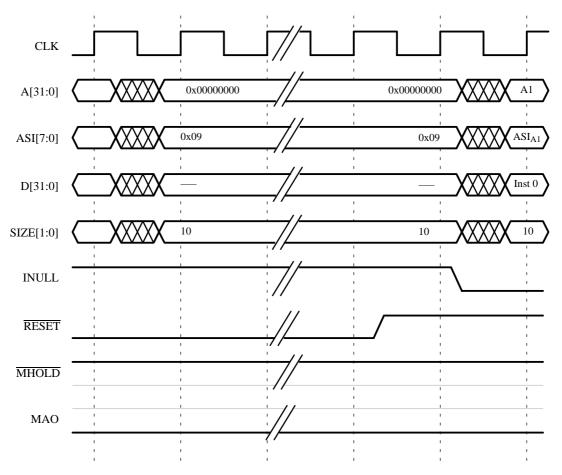

Reset mode is entered whenever the  $\overline{RESET}$  signal is asserted (see Section 3.5). The processor remains in that mode until  $\overline{RESET}$  is deasserted. RESET signal must be asserted nine clocks at least. Upon deassertion, the processor enters execute mode, where the first instruction address to be executed is address 0 in the supervisor instruction address space (see Sections 3.3.3 and 3.4.2.6).

The TSC691E fetches instructions in the execute mode. If the instruction belongs to the floating-point unit or second coprocessor, execution is directed to the appropriate coprocessor. Otherwise, the instruction is executed by the integer unit.

## 3.3.3. Supervisor/User Modes

In support of multitasking, the TSC691E employs a supervisor/user model of operation. The processor is in supervisor mode when the S bit in the Processor State Register (PSR) is set, and in user mode when S is reset (see Section 3.3.4.2). The state of this bit determines which address space is accessed with the ASI bits (see Section 3.4.2.6) and whether or not privileged instructions may be used. Privileged instructions restrict control register access to supervisor software, preventing user programs from accidentally altering the state of the machine.

In non-multitasking situations, such as embedded systems, user (application) code would probably run in supervisor mode to gain access to the PSR's CWP field and other control registers. The only way a program running in user mode may enter supervisor mode is to encounter a software or hardware trap. A return to user mode is accomplished by executing a Return from Trap (RETT) instruction, which restores the state of the S bit to what it was before the trap was taken. A commonly used trap return is the JMPL, RETT delayed control transfer couple (refer to Section 3.4.3.4.4). This restores both the PC and nPC and the previous state of the S bit.

#### 3.3.4. Control/Status Registers

TSC691E control/status registers are all 32 bits wide. The two program counters can only be read to and written to indirectly using such instructions as a CALL, JMPL, software trap (Ticc), and Return from Trap (RETT). The Processor State Register (PSR), Window Invalid Mask (WIM), Trap Base Register (TBR), and multiply-step register (Y), are all read/write registers. Read/write instructions that access the PSR, WIM, and TBR are privileged and thus may only be used in supervisor mode.

Two of these registers, the PSR and TBR, have both read-only status fields and programmable read/write mode fields. In Figure 8 and Figure 10, the read-only status fields appear in lower case italic (for example, *impl*) while the writable mode fields appear in UPPER CASE (for example, PIL).

## 3.3.4.1. Program Counters (PC and nPC)

The Program Counter (PC) contains the address of the instruction currently being executed by the TSC691E, and the next Program Counter (nPC) holds the address (PC + 4) of the next instruction to be executed (assuming there is no control transfer and a trap does not occur). The nPC is necessary to implement delayed control transfers, wherein the instruction that immediately follows a control transfer may be executed before control is transferred to the target address (see Section 3.4.3.4). Having both the PC and nPC available to the trap handler allows a trap handler to choose between retrying the instruction causing the trap (after the trap condition has been eliminated) or resuming program execution after the trap causing instruction.

#### 3.3.4.2. Processor State Register (PSR)

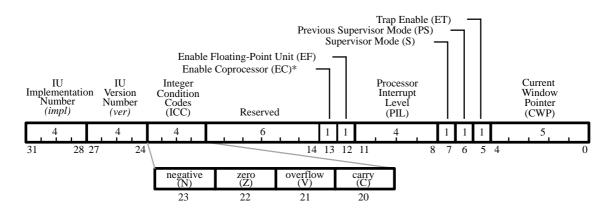

Figure 8. Processor State Register

This is the TSC691E's key status and control register, containing fields that report the status of processor operations or control processor operations. Instructions that modify its fields include SAVE, RESTORE, Ticc, RETT, and any instruction that modifies the condition code field (*icc*). Any hardware or software action that generates a trap will modify the S, PS, and ET fields. The PSR may be read or written directly using the privileged instructions RDPSR and WRPSR. The PSR is made up of the following fields:

#### impl—Implementation

Bits 28 through 31 contain the processor's implementation number. The implementation number for the **TSC691E** is 0001<sub>b</sub>. Writting PSR (WRPSR) does not modify this field.

#### *ver*—Version

Bits 24 through 27 contain the **TSC691E**'s version number. Writting PSR (WRPSR) does not modify this field. The current version number for the **TSC691E** is 0001<sub>b</sub>.

#### icc—Integer Condition Codes

Bits 20 through 23 hold the integer unit's condition codes. These bits are modified by arithmetic and logical instructions whose names end with the letters cc (for example, ANDcc), and can be overwritten by the Writting PSR instruction. The Bicc and Ticc instructions base their control transfer on these bits, which are defined as follows:

#### N-Negative

Bit 23 indicates whether the ALU result was negative for the last icc-modifying instruction.

0 = not negative

1 = negative

#### **Z**—Zero

Bit 22 indicates whether the ALU result was zero for the last icc-modifying instruction.

0 = result was nonzero

1 = result was zero

## V—Overflow

Bit 21 indicates whether an arithmetic overflow occurred during the last *icc*-modifying instruction. The overflow bit is also set if a tagged operation (TADDcc, TSUBcc, etc.) is performed on non–tagged operands (refer to Section 3.4.3.2.3). Logical instructions that modify the icc field always set the overflow bit to 0.

0 = arithmetic overflow did not occur

1 = arithmetic overflow did occur

#### C—Carry

Bit 20 indicates whether an arithmetic carry out of result bit 31 occurred from the last icc-modifying addition or if a borrow into bit 31 resulted from the last icc-modifying subtraction. Logical instructions that modify the icc field always set the carry bit to 0.

0 = a carry/borrow did not occur

1 = a carry/borrow did occur

#### Reserved

Bits 14 through 19 are reserved. A WRPSR should write only 0s to this field.

#### **EC**—Coprocessor Enabled

This bit determines whether the optional second coprocessor is enabled or disabled.

0 = disabled

1 = enabled

If the coprocessor is either disabled or enabled but not present, a CPop, CBccc, or coprocessor load/store instruction will cause a coprocessor-disabled trap. When the CP is disabled, it retains that state until it is re—enabled or reset. Even when disabled, the coprocessor can continue to execute instructions if it contains a queue.

#### EF-Floating-Point Unit Enabled

Bit 12 determines whether the FPU is enabled or disabled.

0 = disabled

1 = enabled

If the FPU is either disabled or enabled but not present, an FPop, FBfcc, or floating-point load/store instruction will cause a floating-point-disabled trap. When disabled, the FPU retains that state until it is re—enabled or reset. Even when disabled, it can continue to execute any instructions in its queue.

#### PIL—Processor Interrupt Level

Bits 8 through 11 identify the processor's external interrupt priority level. The processor will only accept external interrupts whose interrupt level is greater than the value in PIL. Bit 11 of the PIL is the MSB and bit 8 is the LSB.

#### S—Supervisor

Bit 7 determines whether the processor is in supervisor or user mode. Because WRPSR is privileged and only available in the supervisor mode, supervisor mode can only be entered by a software or hardware trap.

0 = user mode

1 = supervisor mode

#### PS—Previous Supervisor

Bit 6 holds the value that was in the S bit at the time the most recent trap was taken.

#### ET—Enable Traps

Bit 5 determines whether traps are enabled. If traps are disabled, all asynchronous traps are ignored. If a synchronous or floating-point/coprocessor trap occurs while traps are disabled, the **TSC691E** halts and enters the error mode (see Section 3.8).

0 = traps disabled

1 = traps enabled

#### **CWP**—Current Window Pointer

Bits 0 through 4 contain a pointer to the currently active register file window. CWP is decremented by traps and the SAVE instruction, and is incremented by RESTORE and RETT instructions.

The Floating-Point Enabled (EF) bit can be used by the programmer to control FPU use when running multiple processes. By disabling the EF bit while running a process that doesn't require the FPU, software would not have to save and restore the FPU's registers across context switches. If the FPU is not present, as signaled by the input signal, FP, the EF bit can be used to provoke floating-point instruction set emulation by generating a floating-point-disabled trap if execution of a floating-point instruction is attempted. This technique may be used with the coprocessor as well.

If it is necessary for the software to manually disable traps, care must be taken when changing the ET bit from enabled (ET=1) to disabled (ET=0), since the RDPSR, WRPSR instruction sequence is interruptible. One way to handle that is to write all interrupt trap handlers so that before they return program control to the supervisor software that was interrupted, they restore the PSR to the value it had before the interrupt was taken. This will guarantee a correct result when the interrupted RDPSR, WRPSR sequence continues. The only PSR bit that cannot be restored is the PS bit, which is overwritten when the trap is taken.

An alternative to the RDPSR-WRPSR sequence is to generate a "trap instruction" trap with a Ticc instruction. A taken trap automatically sets ET to 0, disabling further traps.

#### 3.3.4.3. Window Invalid Mask Register (WIM)

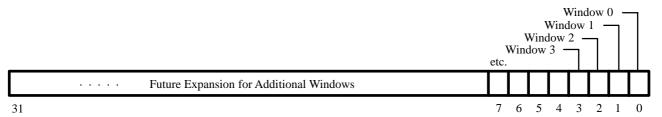

Figure 9. Window Invalid Mask

This register designates which window(s) will cause generation of an underflow or overflow trap when pointed to by the CWP as the result of a SAVE, RESTORE, or RETT instruction.

Each bit in the WIM register (see Figure 9) corresponds to a window; if a bit is set to 1, the window corresponding to that bit is marked as invalid. If a SAVE, RESTORE, or RETT instruction would cause the CWP to point to a window whose WIM bit equals 1, a window overflow (SAVE) or window underflow (RESTORE, RETT) trap is generated. The trap handler uses the *local* registers of the invalidated window.

A WIM bit is usually set by the operating system software to identify the boundary between the oldest and newest window. The overflow or underflow trap prevents previous windows from being overwritten or restores previous windows from memory. WIM can also be used to mark off register banks for fast context switching (see Section 3.3.1.1.3).

WIM is read by the RDWIM instruction, and written by the WRWIM instruction. Bits corresponding to unimplemented windows read as zeros and are unaffected by writes.

The WIM register is NOT cleared during reset. It must be initialized by software.

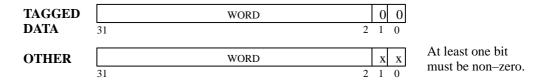

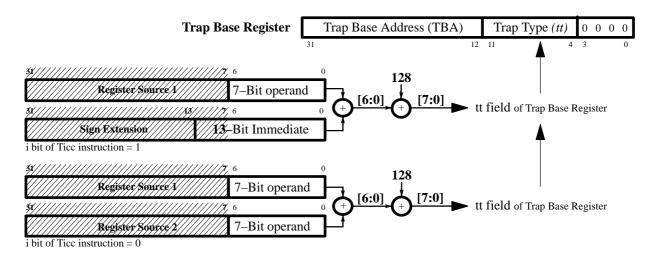

#### 3.3.4.4. Trap Base Register (TBR)

Figure 10. Trap Base Register

When a trap occurs, the program counter (PC) is loaded with the contents of the trap base register. The TBR contains two fields that together constitute a pointer into the trap table, which in turn contains the trap handler address (see Figure 10). RDTBR can read the entire register; however, the WRTBR instruction can write only to the Trap Base Address field. Only hardware can write to the Trap Type field, and bits 0 through 3 are zeros and are unaffected by a write. The Trap Type field can be directly manipulated using the Ticc instruction. For more information on trap operation, see Section 3.8.

#### **TBA**—Trap Base Address

Bits 12 through 31 contain the most-significant 20 bits of the trap table address. This field applies to all trap types except reset, which forces address 0. The TBA is software controlled.

#### *tt*—Trap Type

Bits 4 through 11 comprise the Trap Type field, an eight-bit value that provides an offset into the trap table based on the type of trap being taken (see Section 3.8.5.3). This field retains its value until the next trap is taken.

#### **3.3.4.5.** Y Register

The Y register is used by the multiply step instruction (MULScc) to create 64-bit products. This register is read and written using the non-privileged RDY and WRY instructions.

#### 3.3.5. Data Types

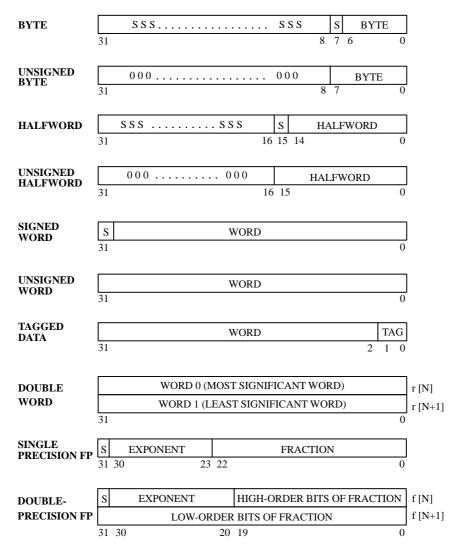

The TSC691E supports ten data types (eleven with extended-precision floating-point, see Section 3.3.5.3). Integer types include byte, unsigned byte, halfword, unsigned halfword, word, unsigned word, doubleword, and tagged data. ANSI IEEE 754-1985 floating-point types include single- and double-precision. A byte is 8 bits wide, halfwords are 16 bits, words and single-precision floating-point are 32 bits, doublewords and double-precision floating-point are 64 bits. Table 2 shows the formats for single-precision and double-precision floating-point numbers.

#### **Table 2. Floating-Point Formats**

#### Single-Precision Floating-Point Format

| s = sign (1)<br>e = biased exponent<br>f = fraction (23) | (8)                   |                                                                                                                                                                                                 |

|----------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| normalized number subnormal (e = 0): zero (e = 0):       | $f \neq 0$            | (-1) <sup>s</sup> * 2 <sup>e-127</sup> * 1.f<br>(-1) <sup>s</sup> * 2 - <sup>126</sup> * 0.f<br>(-1) <sup>s</sup> * 0                                                                           |

| signaling NaN:<br>quiet NaN:<br>infinity:                | $f \neq 0$ $f \neq 0$ | s = u; e = 255 (max); f = .0uu···uu<br>(at least one bit must be nonzero)<br>s = u; e = 255 (max); f = .1uu···uu<br>s = 0 or 1, depending upon sign;<br>e = 255 (max); f = .00···00 (all zeros) |

### Double-Precision Floating-Point Format

```

s = sign(1)

e = biased exponent (11)

f = fraction (52)

(-1)^s * 2^{e-1023} * 1.f

normalized number (0 < e < 2047):

(-1)^{s} * 2 - 1022 * 0.f

subnormal (e = 0): f \neq 0

(-1)^{s} * 0

zero (e = 0):

f \neq 0

signaling NaN:

f \neq 0

s = u; e = 2047 (max); f = .0uu \cdots uu

(at least one bit must be nonzero)

quiet NaN:

f \neq 0

s = u; e = 2047 (max); f = .1uu···uu

s = 0 or 1, depending upon sign;

infinity:

e = 2047 \text{ (max)}; f = .00...00 \text{ (all zeros)}

```

# 3.3.5.1. Data Organization In Registers

The organization of the ten data types when loaded into registers is shown in Figure 11.

Figure 11. Processor Data Types

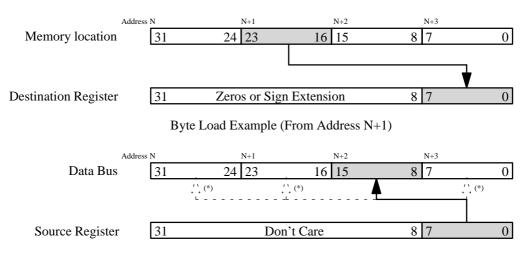

When moving memory data to or from the registers, byte operands are always loaded to or extracted from the lower eight bits of a register. On a load, bits 8 through 31 are sign-extended for a byte or zero-extended for an unsigned byte. Halfwords are always loaded to or extracted from the lower 16 bits of a register. Bits 16 through 31 are sign-extended for a halfword or zero-extended for an unsigned halfword during a load. All 32 bits of a signed or unsigned word are loaded from or stored to memory. Stores of byte and halfword data are not sign-extended. Tagged data is handled as an unsigned word. Doubleword operands load to and store from two contiguous registers, r[n] and r[n+1], with r[n] containing the most significant word. Figure 12 illustrates the relationship between the way data is stored in memory and the way it is loaded into registers.

For single-precision, floating-point operands, bit 31 contains the sign bit, bits 23 through 30 contain the eight bits of exponent, and bits 0 through 22 contain the 23-bit fraction. Double-precision operands require a register pair, with the upper-order register r[n] containing the sign bit, 11-bit exponent, and the high-order bits of the fraction. The lower-order register r[n+1] contains the low-order bits of the fraction. Total fraction size is 52 bits.

When loading doublewords or double-precision operands from memory to the working registers (either r or f), the destination register must be at an even address or the hardware will force such an address. For example, an attempted load double to register r[9] would be forced to r[8], so that the most significant word would be loaded in r[8] and the least significant word in r[9]. A load double to r[0] would result in the loss of the most significant word.

(\*) The irrelevant bytes of the data bus are filled with the stored data byte (idem for halfword)

Byte Store Example (To Address N+2)

Figure 12. Byte Operand Load and Store

#### 3.3.5.2. Data Organization In Memory

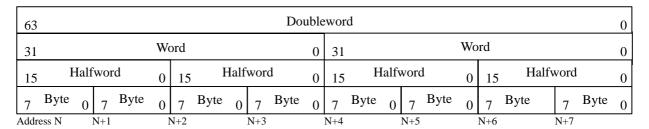

Organization and addressing of data in memory follows the "Big-Endian" convention wherein lower addresses contain the higher-order bytes (see Figure 13).

For a stored word, address N corresponds to the most significant byte of the word, and address N+3 corresponds to the least significant byte. The address of a halfword, word, or doubleword is also the address of its most significant byte. A halfword datum must be located on a halfword boundary (address bit [0] = 0), which is evenly divisible by 2. Similarly, a word must be located on a word boundary (address bits [1:0] = 0) evenly divisible by 4, and a doubleword must be located on a doubleword boundary (address bits [2:0] = 0) evenly divisible by 8. Attempting to access misaligned data will generate a "memory\_address\_not\_aligned" trap.

Figure 13. Data Organization in Memory

#### 3.3.5.3. Extended Precision

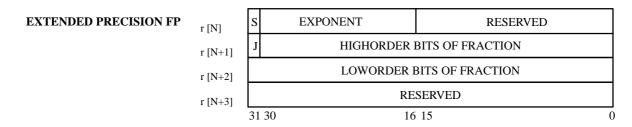

The SPARC architecture supports another data type, an ANSI/IEEE 754-1985 extended-precision floating-point type with a width of 128 bits (see Table 3 ). When loaded to the working registers, extended-precision operands require a register quadruple (see Figure 14 ). The upper-order register r[N] contains the sign bit, a 15-bit exponent, and a 16-bit reserved field. The next register r[N+1] contains the one-bit integer part and 31 high-order bits of the fraction. The next register r[N+2] holds the 32 low-order bits of the fraction. Total fraction size is 63 bits. The fourth extended-precision register r[N+3] is reserved. As with double-precision operands, when loading an extended-precision operand, the destination register must be at an even address or the hardware will force an even address.

The memory address of an extended-precision datum is also the address of its most significant byte (see Figure 15). An extended-precision datum must be located on an extended-precision boundary (address bits [3:0] = 0), which is evenly divisible by 16.

Table 3. Extended-Precision Floating-Point Format

| j = integer part (1)                                                        | e = biased exponent (15)  |                                                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| normalized number ( 0 subnormal number ( e zero ( $s = 0$ ; $e = 0$ ) ( $f$ | $= 0; j = 0) (f \neq 0):$ | (-1) <sup>s</sup> * 2 <sup>e-16383</sup> * j.f<br>(-1) <sup>s</sup> * 2 <sup>-16382</sup> * j.f<br>(-1) <sup>s</sup> * 0 |  |  |  |  |

| signaling NaN:                                                              | $f \neq 0$                | s = u; e = 32767 (max); j = u;<br>f = .0 uu···uu (at least one bit must be<br>must be nonzero)                           |  |  |  |  |

| quiet NaN:                                                                  | $f \neq 0$                | s = u; e = 32767 (max); j = u;<br>f = .1 uu···uu                                                                         |  |  |  |  |

| infinity:                                                                   |                           | s = 0 or 1, depending upon sign;<br>e = 32767 (max); j = u;<br>f = .00 00 (all zeros)                                    |  |  |  |  |

Figure 14. Extended-Precision Data Organization in Registers

| 128       | 128 Extended – Precision Data |   |     |      |   | 0      |       |   |      |      |   |

|-----------|-------------------------------|---|-----|------|---|--------|-------|---|------|------|---|

| 63        | Doubleword 0 63               |   |     | 63   | Ι | Double | eword |   | 0    |      |   |

| 31        | Word                          | 0 | 31  | Word | 0 | 31     | Word  | 0 | 31   | Word | 0 |

| Address N |                               |   | N+4 |      |   | N+8    |       |   | N+12 |      |   |

Figure 15. Extended-Precision Data Organization in Memory

## 3.4. Instruction Set

This section describes the TSC691E instruction set as defined by the SPARC architecture. Included are subsections on instruction formats, addressing, instruction types, and an op code summary. A specific document, SPARC V7.0 Instruction Set contains a description of the assembly language syntax and a complete set of instruction definitions.

#### **3.4.1. Instruction Formats**

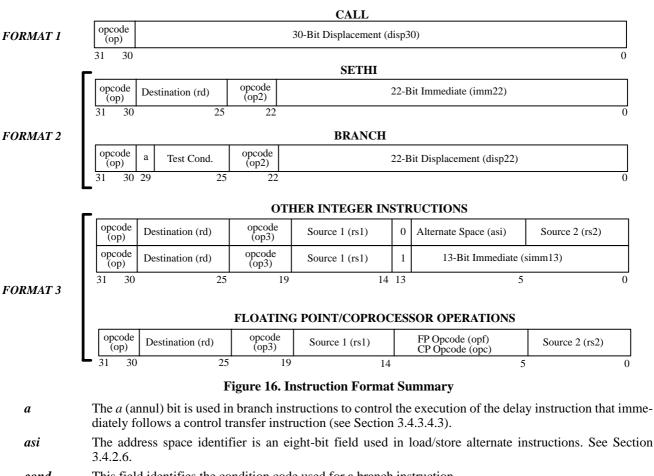

There are only three basic instruction formats plus three subformats. Format 1 is used for the CALL instruction, format 2 for the SETHI [1] and Branch instructions, and format 3 for the remaining integer and floating-point/coprocessor instructions. Figure 16 shows each format with its fields, bit positions, and the instructions that use that format. All instructions are one word long and aligned on word boundaries in memory. For most instructions, operands are located

in source registers (represented by *rs1* and *rs2*). The remaining instructions use one source register plus a displacement or immediate operand contained within the instruction itself.

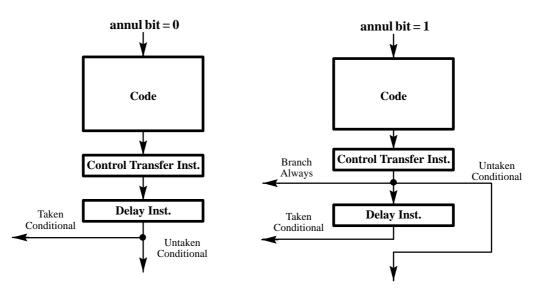

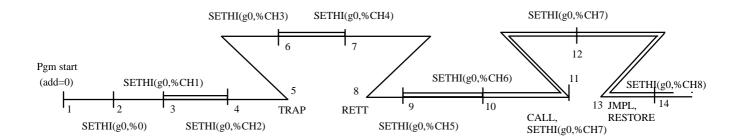

See chapter 4.2 for application of this instruction in Program Flow Control.

*cond* This field identifies the condition code used for a branch instruction.

disp22 This field contains the 22-bit displacement value used for PC-relative addressing for a taken branch. It is sign extended to full-word size when used.

disp30 This field contains the 30-bit displacement used for the PC-relative addressing of a CALL instruction.

*i* The *i* (immediate) bit determines whether the second ALU operand (for non-FPop instructions) will be r[rs2] (i = 0), or a sign-extended *simm13* (i = 1).

*imm22* This field contains the 22-bit constant used by the SETHI instruction. (See Chapter 4.2 for Program Flow Control)

*op* The *op* field selects the instruction format as shown in Table 4.

op2 The op2 field (Table 5) contains the instruction opcode for format 2 instructions (op=0).

op3 The 6-bit op3 field contains the instruction opcode for a format 3 instruction (op = 2 or 3).

**opc** The 9-bit *opc* identifies a coprocessor-operate (CPop) instruction. The relationship between the *opc* field and CPop instructions is described in Section 3.4.3.6.

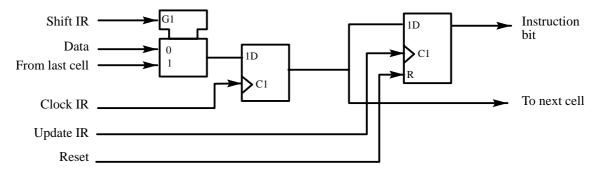

**opf** The 9-bit **opf** identifies a floating-point-operate (FPop) instruction. The relationship between the **opf** field and FPop instructions is described in Section 3.4.3.6.